|

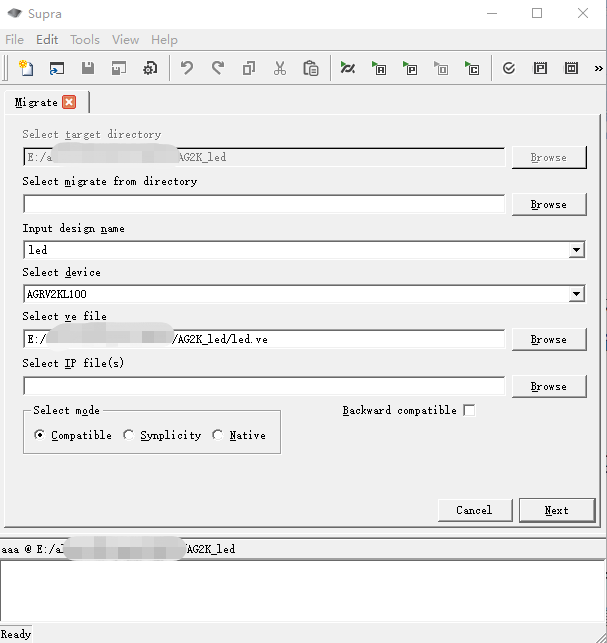

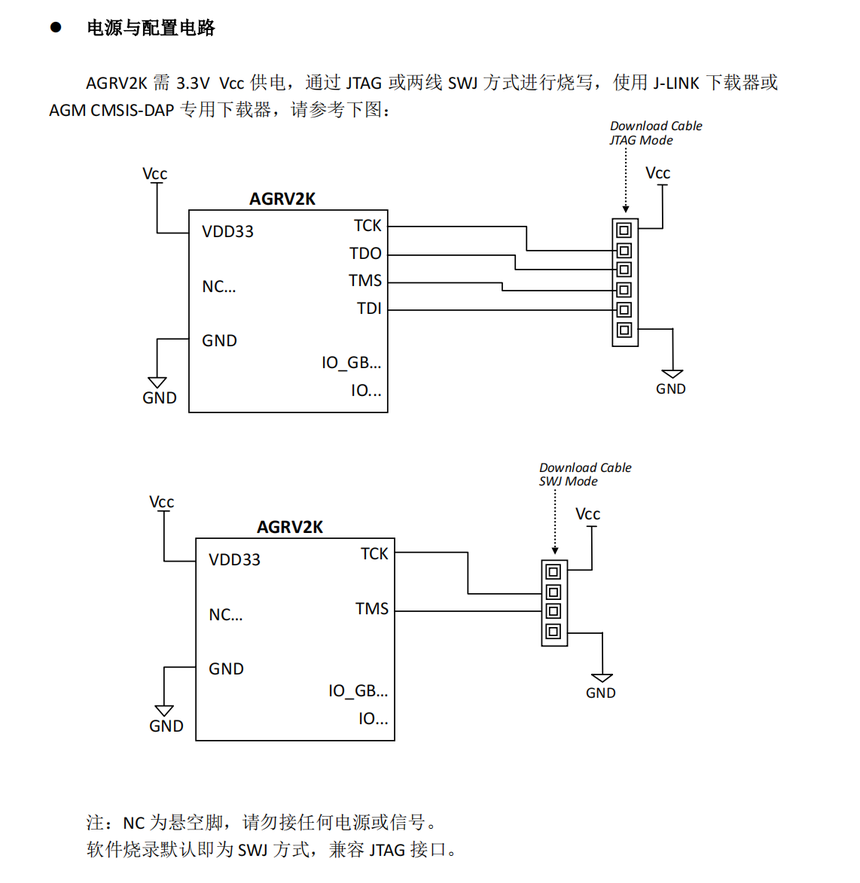

AGRV2K开发流程(官方版)附:DEMO (7月更新) 软件开发流程 1.)软件安装: 解压缩或执行安装文件,安装 Supra 软件。执行文件为 bin 目录中的 Supra.exe。 运行 Supra,选择菜单 File -> Import license,选择 license 文件并导入 License。 2.)新建项目: 新建一工程目录。打开 Supra,在目录中新建 project。 进入 Tools -> Migrate:

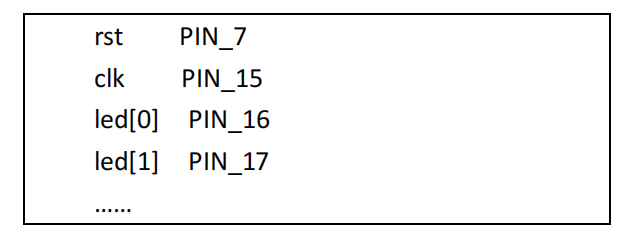

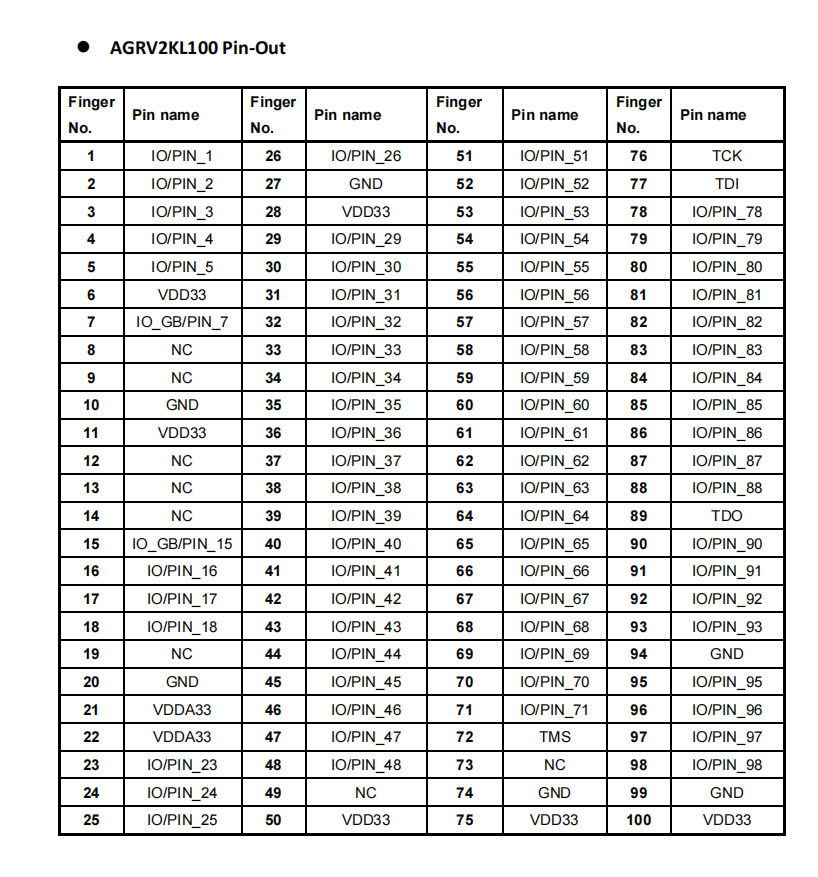

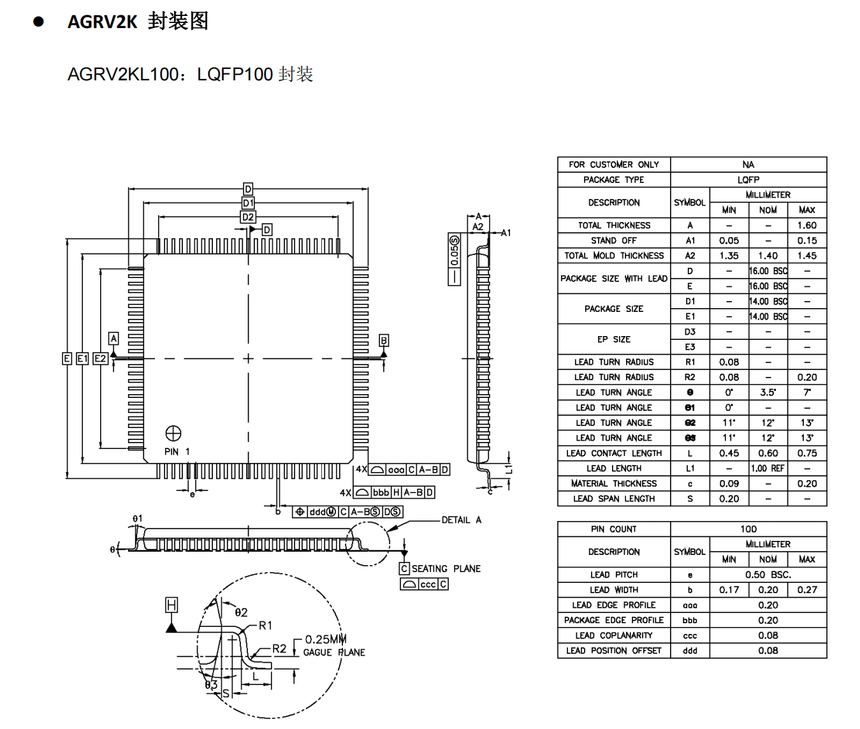

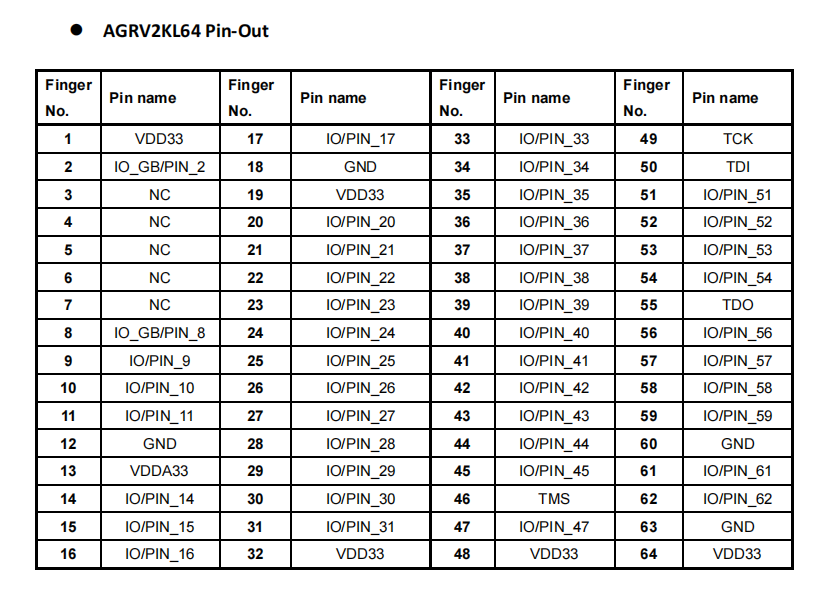

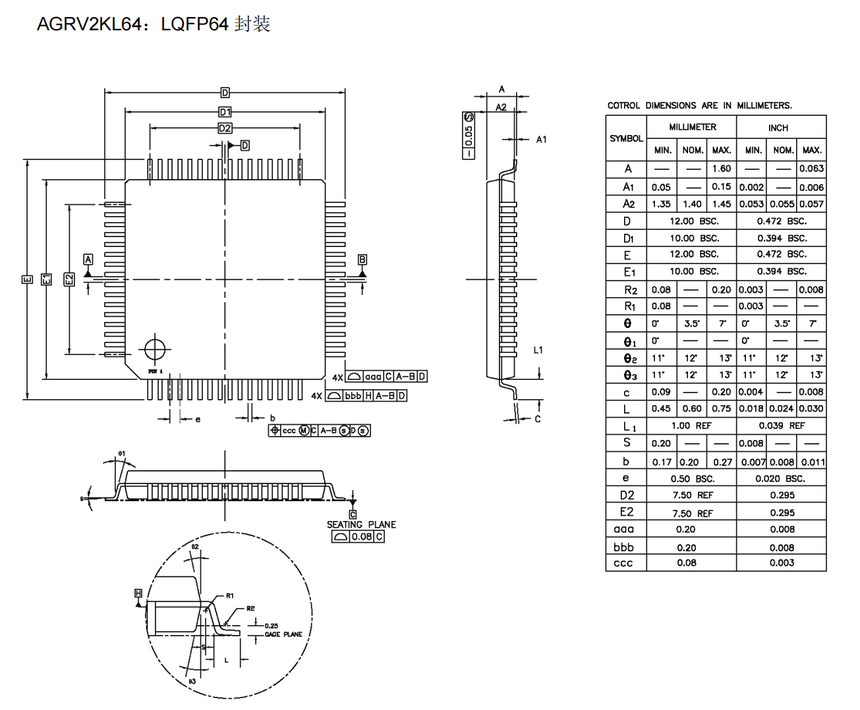

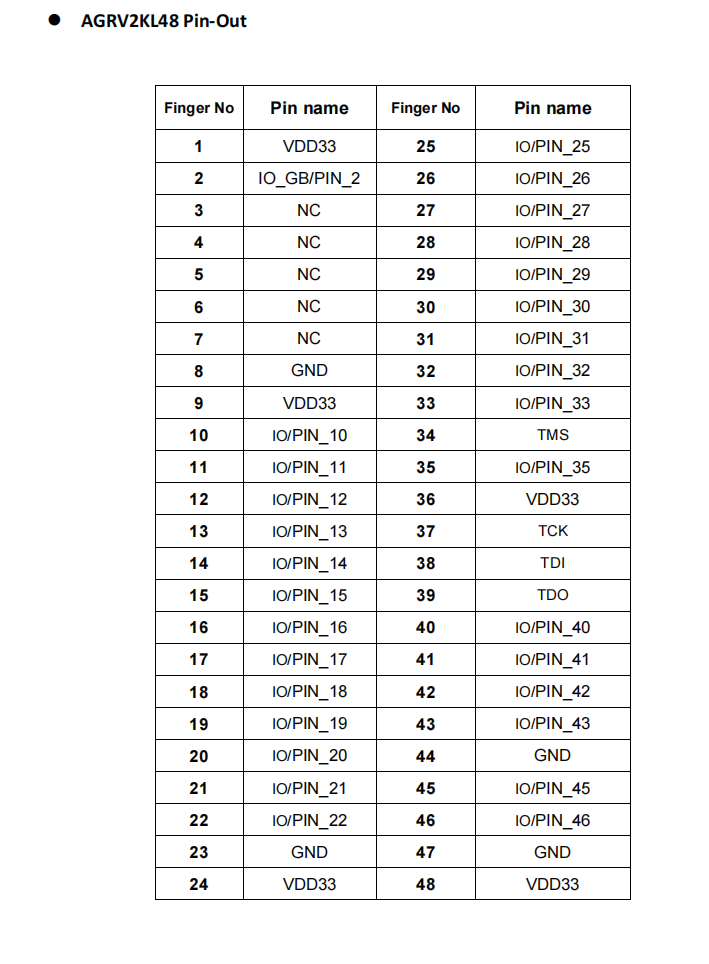

Target Directory 默认为新建的工程目录,Migrate from directory 不填,输入设计名称(这里 例如 led),Device 选 AGRV2K 系列型号。选择 ve 文件(管脚分配文件)。IP 文件不用填。 选择对应开发 Mode:Native 选项(AGM 自有 EDA 综合工具),Synplicity 选项(第三方综 合工具,例如 Synplify,Mentor 等),Compatible 选项(兼容 Altera Quartus II 的综合工具)。 下面主要介绍 Supra 基于 Quartus II 综合的设计流程,其它工具设计流程类似。Mode 选择 Compatible,点 next, 生成一个以 led 命名的 Quartus II 项目,以及空的设计文件(qpf,v, sdc 等)。 ve 文件为 IO 管脚位置设置,可通过任意文本编辑器自行编辑产生。管脚名称请参考前面的 管脚说明表格(PIN_1,PIN_2 格式),全局信号最好选 IO_GB 管脚。 ve 文件格式如下(管脚设计名称+空格+封装管脚名称,#为注释符):

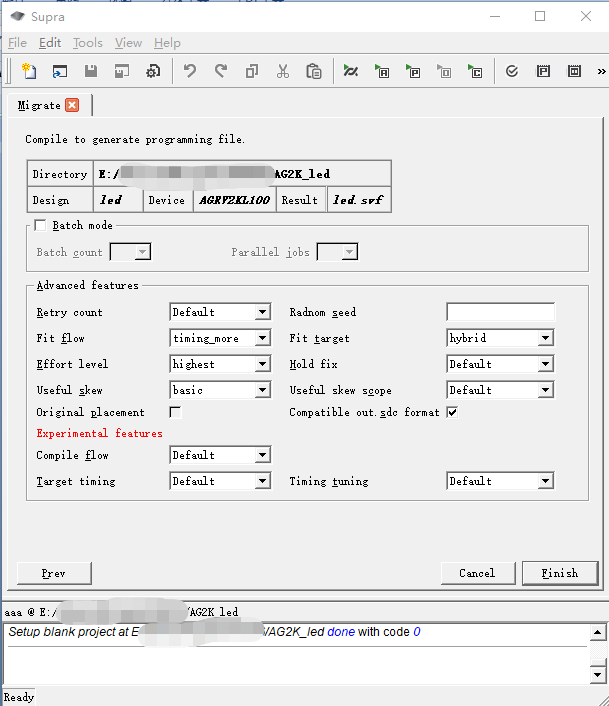

3.)项目设计: 用 Quartus II 打开 led.qpf 项目文件,工程已设置好,不要修改型号。默认为 EP4CE75,如果 Quartus II 没有这个器件,需要先安装 Cyclone IV 系列器件库。 空的项目中加入你的设计文件.v,或添加其它类型设计文件。 设计完成后,Quartus II 中选择菜单中 Tools -> Tcl Scripts...,窗口中选 af_quartus.tcl,点击 Run 进行编译,综合后产生所需网表文件 4.)项目编译: Supra 里继续执行 Next,开始进行编译。编译选项,默认即可。

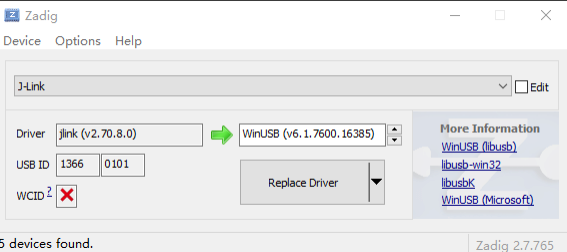

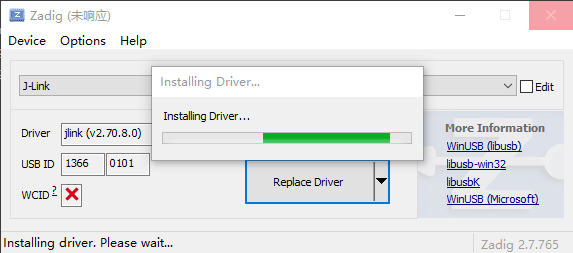

编译成功后即可得到最终烧写文件,led.bin。 如未改变工程路径,修改设计代码后,Quartus 里只需执行正常的编译(Start Compilation), 可以不用再运行 af_quartus.tcl 文件。然后在 Supra 中打开 Tools -> Compile,完成编译即可。 5.)安装 JLINK 驱动 运行 supra 目录中提供的 zadig-2.8.exe 文件,点击菜单 Options - List all devices,选择下面的 Jlink。有的版本 Jlink 会显示为 BULK…等,驱动显示为已安装的原 Jlink 驱动。

点击 Replace Driver 按键,把 Jlink 原驱动替换为 WinUSB 版本。

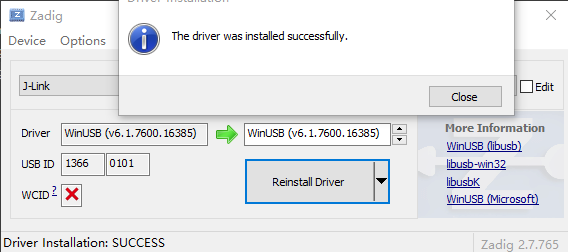

安装成功后,Jlink 驱动显示 WinUSB。

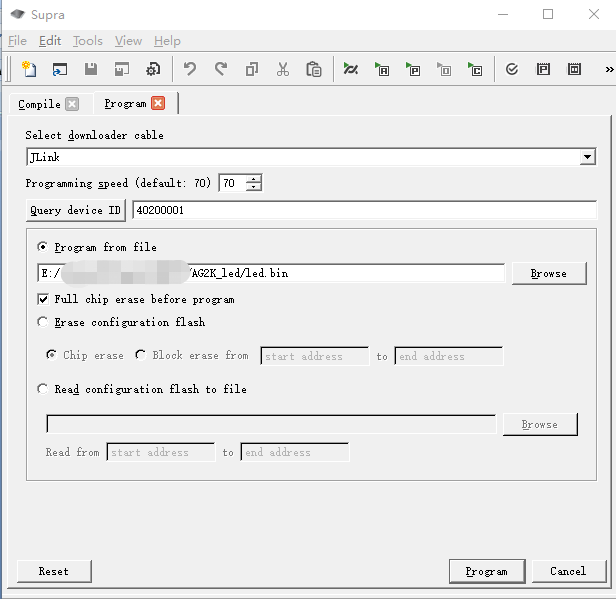

6.)芯片烧写: Supra 软件中选 Tools –> Program,下载线选 JLINK 或 CMSIS-DAP。速度默认即可。 可以先点击 Query device ID,查看是否检测到器件,正确 ID 为:40200001 选择编程文件 led.bin,点击 program 开始烧写文件。如没有出现错误信息,显示“done with code 0”,即烧写成功,程序开始运行。

需要获取更多的资料和支持可以联系我们 提供“芯片测样-发送资料-技术支持-批量采购” 联系方式: 姚工 13661545024(VX同号) (加的时候备注下公司名和个人名字) 在线商城:agm-micro.taobao.com 公司网站:www.agm-micro.com 资料网站: www.tcx-micro.com |