重要更新,好消息

AGRV2K系列型号,开发可使用最新版本的supra直接开发了(目前仅支持Verilog设计)

⚫ 软件开发流程

Supra下载——

链接:https://pan.baidu.com/s/1Q-bA_pe8GVpRWMpeICmQaQ?pwd=1234

提取码:1234

(下载最新版)

1.)软件安装:

解压缩或执行安装文件,安装 Supra 软件。注意安装目录不能有中文或空格。执行文件为bin 目录中的Supra.exe。

运行Supra,选择菜单 File -> Import license,选择 license 目录中的licence.txt 文件并导入。

2.)新建项目:

新建一工程目录,路径同样不能有中文或空格。打开Supra,在该目录中新建 project,设置

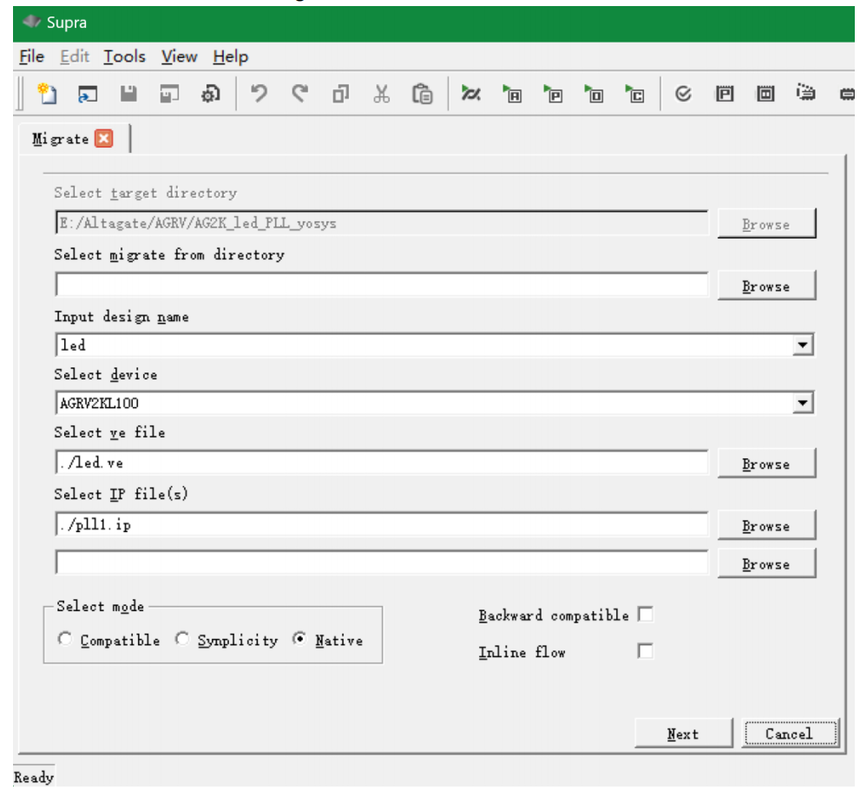

项目目录和名称。进入Tools -> Migrate:

Target Directory 默认为新建的工程目录,Migrate from directory 不填,输入设计名称(这里范例名称为led),Device 选AGRV2K 系列型号。选择 ve 文件(管脚分配文件) 。IP 文件为预先产生的PLL、RAM 等IP,没有可以不用填。

选择对应开发Mode:Native 选项(AGM Supra 综合工具),Synplicity 选项(第三方综合工具,

例如Synplify,Mentor 等) ,Compatible 选项(兼容Altera Quartus II 的综合工具)。

下面主要介绍 Native mode 的设计流程,这个流程仅支持 Verilog 语言的设计输入。如使用Compatible 设计方式,可参考3.0 版本Manual 文档。

Mode 默认选择 Native,点 next,进入下一步。

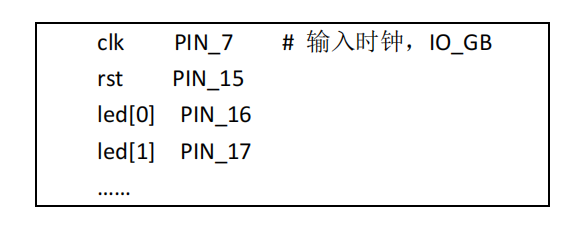

其中的ve 文件为IO 管脚位置设置,可通过任意文本编辑器自行编辑产生。管脚名称请参考前面的管脚说明表格(PIN_1,PIN_2 格式),全局时钟信号或PLL 输入时钟要选IO_GB 管脚。

ve 文件格式如下(管脚设计名称+空格+封装管脚名称,#为注释符):

3.)项目设计:

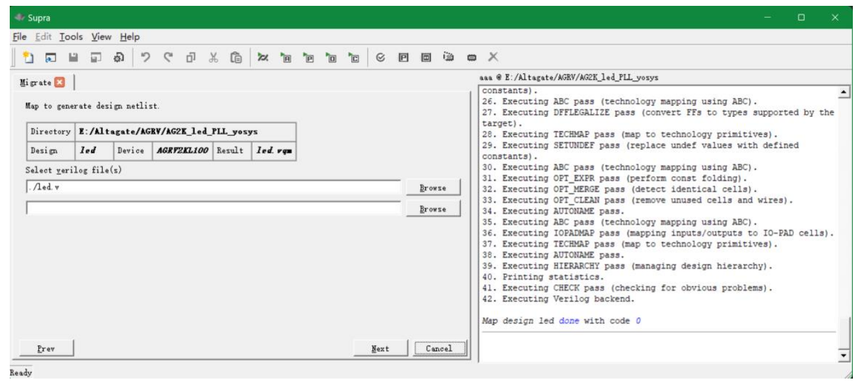

这一步为加入项目的设计文件,包括用到的所有Verilog(*.v)文件,可添加多个文件。

点击Next,会进行综合并产生网表文件.vqm,没有出错则继续Next 下一步。

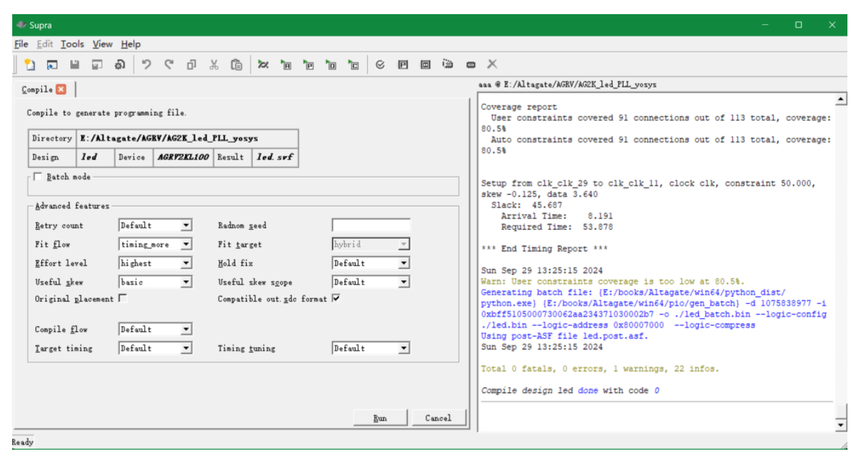

4.)项目编译:

Supra 里继续执行 Next,开始进行编译。编译选项,默认即可。如果只是重复编译,也可以

在Tools->Compile 菜单里直接打开这个编译界面。

编译成功后即可得到最终烧写文件,led.bin。

Win10/11 OS 下,编译最后一步会利用Python 功能产生led_batch.bin。这是用于离线烧录的芯片完整bin 文件。如果 WIN7 或以下OS,最后这步会出错,如已产生 led.bin,可以先忽略。

在supra 中可正常烧录的。

6.)芯片烧写:

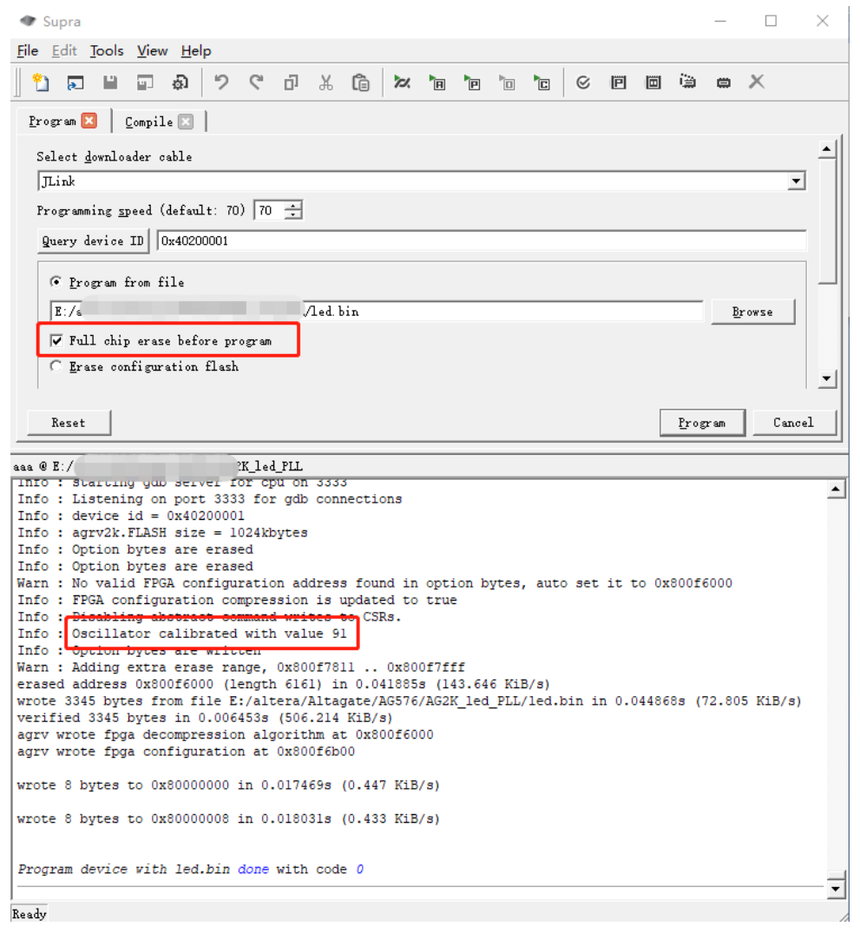

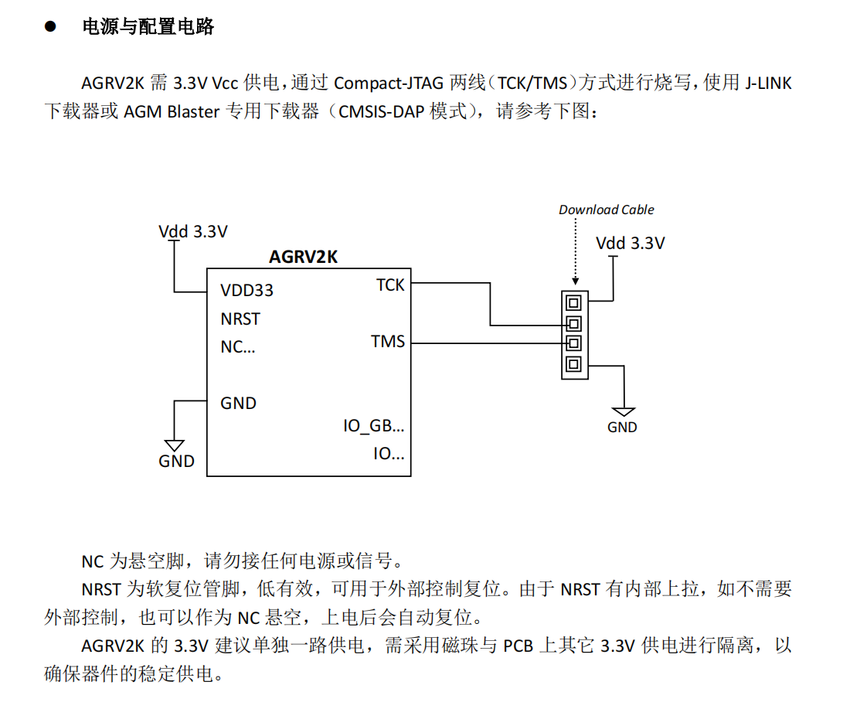

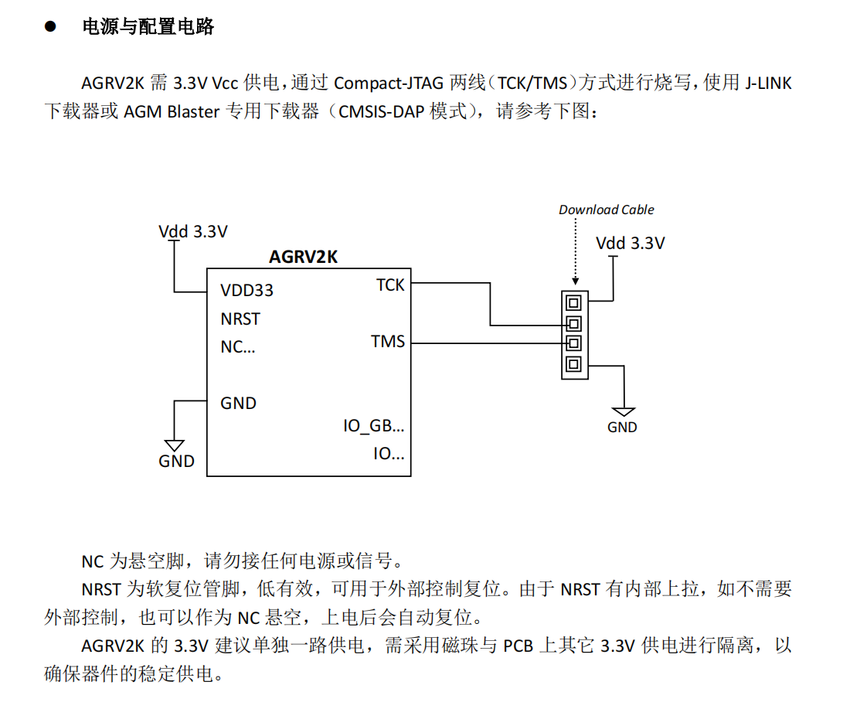

Supra 软件中选Tools –> Program,AGRV2K 仅支持 JLINK 或CMSIS-DAP,选择正确的Cable。

速度默认即可。

可以先点击Query device ID,查看是否检测到器件,正确 ID 为:40200001

选择编程文件led.bin,点击program 开始烧写文件。如没有出现错误信息,显示“done with code 0” ,即烧写成功,程序开始运行。

勾选下面的Full Chip erase before program,可以在烧录前擦除芯片程序,并写入默认设置启动项。

勾选Lock after program,则芯片烧录后打开加密锁功能,无法读取出内部程序数据。

另外,可以选择Erase 功能,进行程序的擦除。

⚫ 安装下载器驱动

AGRV2K 的下载器仅支持 JLINK 或 AGM DAP-LINK。

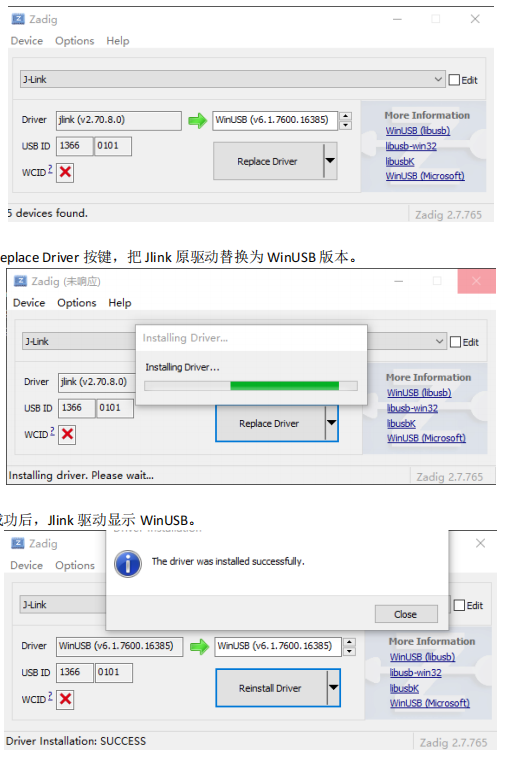

WIN 下JLINK 需安装驱动。 运行supra 目录中提供的zadig-2.8.exe 文件,点击菜单Options - List all devices,选择下面的 Jlink。有的版本Jlink 会显示为BULK…等,驱动显示为已安装的原 Jlink驱动。

WIN10 及以上 OS,DAP-LINK 免安装驱动。WIN7 中同样需要按上述流程给 DAP-LINK 安装驱动。

⚫ 内部 IP 的使用

1.)PLL

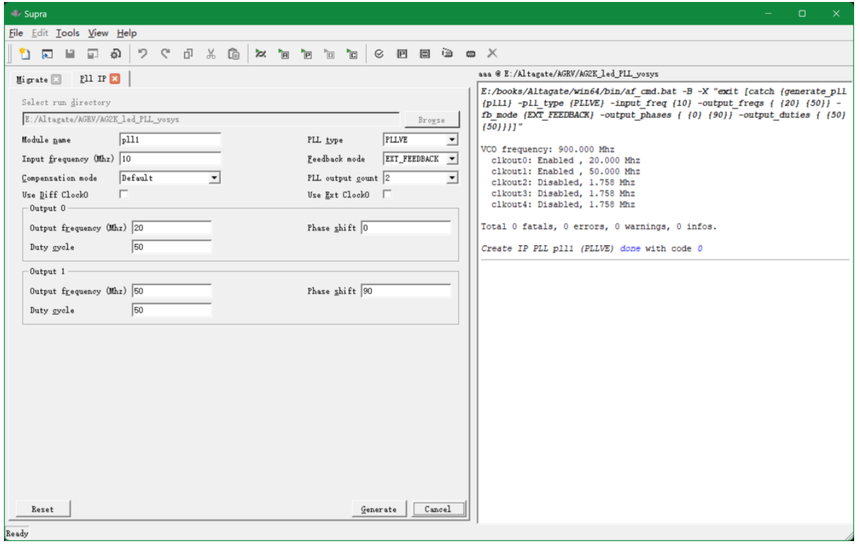

AGRV2K 器件支持1 个PLL。在Supra 中添加 IP(Tools -> Create IP -> Create PLL) 。

PLL 输入时钟管脚要选 IO_GB 管脚,即全局时钟管脚。否则编译会出错,无法布线到 PLL 输入信号。

PLL IP 名称可以自定义,Type 要用PLLVE,Feedback Mode 这里可忽略。然后根据设计需要选择补偿模式,输入输出时钟的特性要求。

点击Generate 按钮,即可产生 ip 文件。

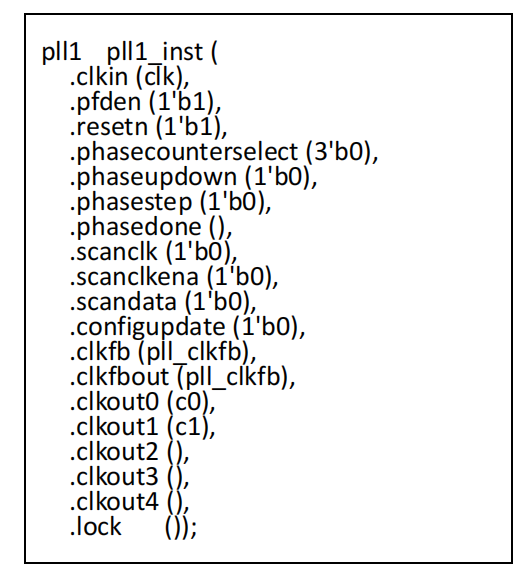

Verilog 文件中调用 IP,可参考下面代码。一般只需用到 clkin,resetn,clkout 和 lock,注意clkfb 和 clkfbout 需直连,其它信号按如下代码默认设置即可。

2.)RAM

AGRV2K 器件支持4 个M9K Block (1K Byte),共 4K Byte 空间。 同样在Supra 里 Create Memory IP。Type 选择 BRAM9K,总共不要超过4K Byte 的容量。可根据需要选择单口,双口等属性。

3.)内部晶振

AGRV2K 器件内部有一 8MHz 晶振,可作为逻辑设计的时钟输入,也可接入 PLL,并支持精度自校准。

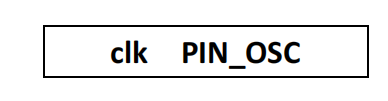

设计中使用这个晶振的时钟输入,需要在ve 文件中指定时钟输入管脚位置为PIN_OSC,如:

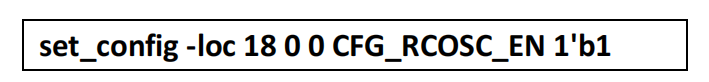

并在项目的设置文件,如led.asf 中加入语句:

工程编译完成后,烧录界面,Program 需选择“Full chip erase before program”。

Program 后显示的信息中包含“Info : Oscillator calibrated with value xx”即表示内部晶振已打开并校准,可以正常使用。

某些JLINK 下载器时钟精度较差,利用 JLINK 校准后,时钟输出频率会偏差较大。建议用 AGM DAP-LINK。

⚫ IO 特性设置

在工程的设置文件(*.asf,默认为空的文本文件)中加入相关语句,可以设置如下 IO 特性。

这里xxx 为代码中 IO 的名称。

1.)上拉电阻:

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to xxx

2.)下拉电阻:

set_instance_assignment -name CFG_KEEP -to xxx 2’b01 -extension

3.)驱动电流:

set_instance_assignment -name CURRENT_STRENGTH -to xxx 8MA

默认是8MA,可以设置范围 2-30mA,偶数值。

注意:上边一行添加完后,务必在后边添加回车换行(保证这行不是文件最后一行)。

需要获取更多的“资料”和“支持”和“批量采购”可以联系我们

提供“芯片测样-发送资料-技术支持-批量采购”

联系方式: 姚工 13661545024(VX同号)

(加的时候备注下公司名和个人名字)

在线商城:agm-micro.taobao.com

公司网站:www.agm-micro.com

资料网站: www.tcx-micro.com