|

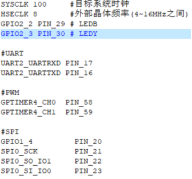

AGRV2KLxx使用入门(6月更新)AGRV2KLxx使用入门 一、 环境搭建 在开始FPGA代码编程之前,必须熟悉Vscode下的PlatformIO的开发环境。对AGM定义的VE文件的格式要有一定的了解。AGM的MCU的pin功能定义,除了晶体、复位、电源、地、模拟(包括ADC, DAC, CMP),其它所有的数字IO都可以通过VE文件来任意定义。 1. VE文件格式

说明: l VE文件格式为每个引脚一行,每行由Function pin和Device pin组。芯片内部具体有哪些信号线可以参见《AGRV2K_逻辑设置.pdf》。 l 外部晶体建议使用4~16MHz之间。AGM的MCU不建议使用内部晶体,内部晶体偏差较大。\ 2. ini文件格式 该文件的大部分内容解释参见《AGM在VSCode下的使用入门.pdf》。下面只介绍与FPGA相关部分。

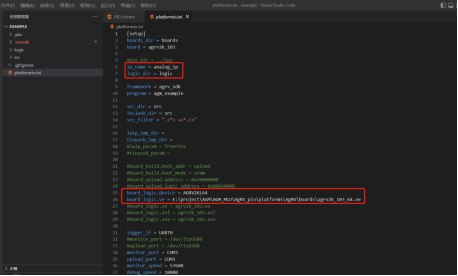

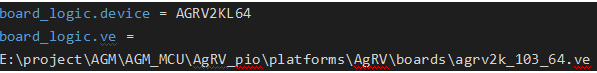

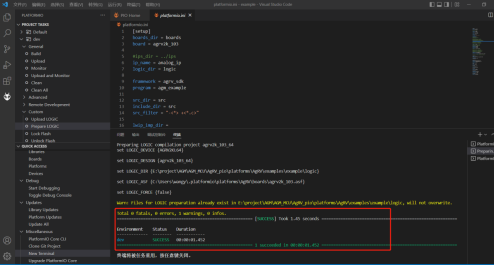

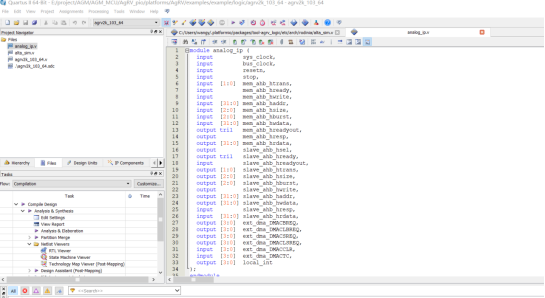

如上图所示:

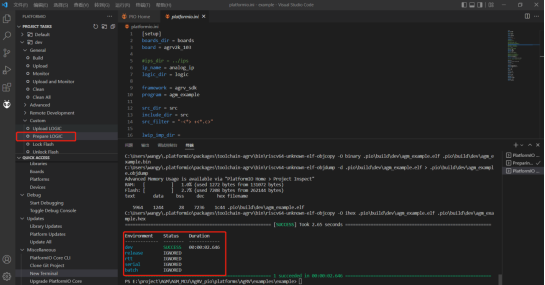

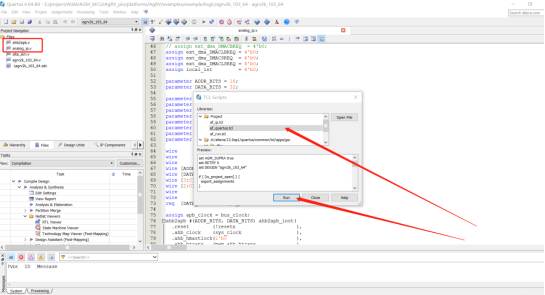

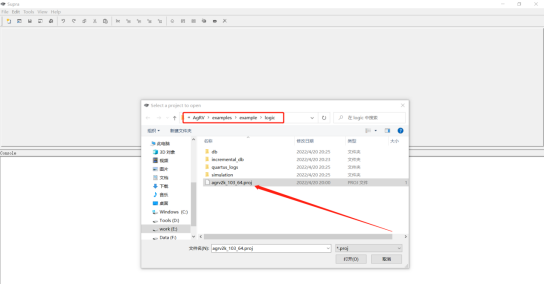

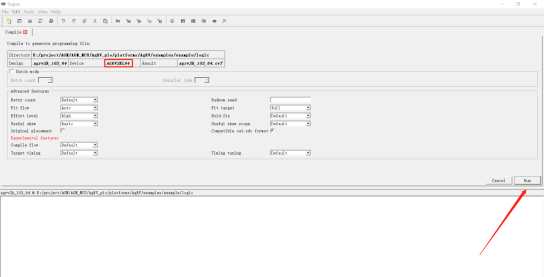

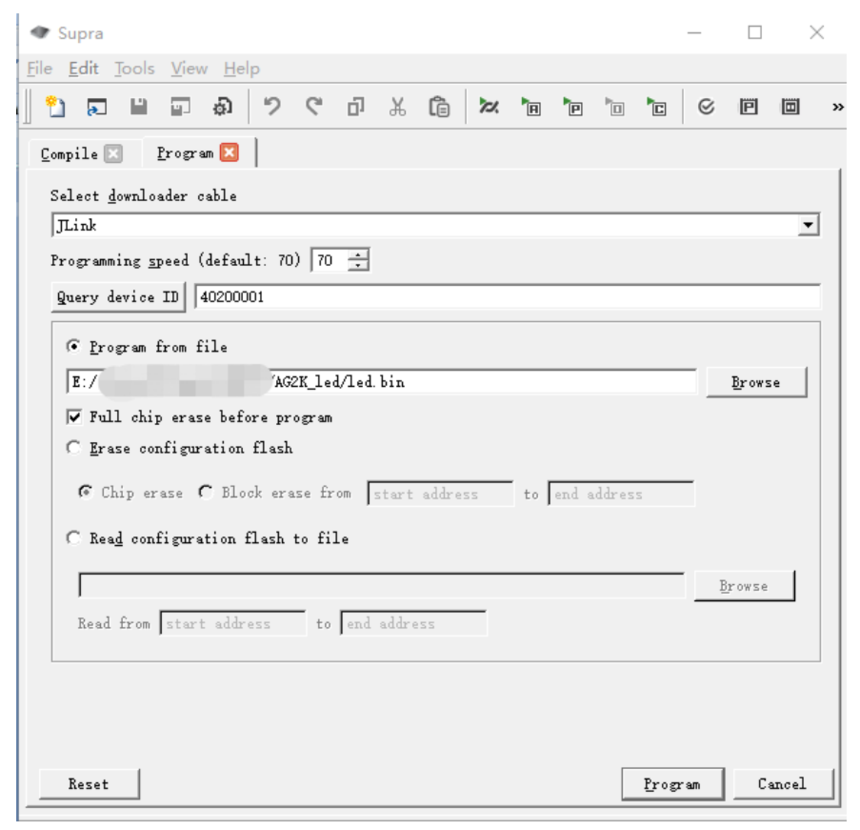

ip_name是用户自定义的逻辑块名称。Logic_dir是在工程当前目录下创建的一个目录,存放所有FPGA的相关代码。 board_logic.device是内部FPGA的型号,这里需要注意如果是100pin的,使用AGRV2KL100。 board_logic.ve 是使用的VE文件的绝对位置。不清楚如何使用相对目录,暂时只能用绝对位置。这里使用了agrv2k_103_64.ve,后面的64表示64pin。因为100pin与64pin的定义是不同,需要加以区别。 以上确认无误后,需要在PlatformIO下对工程进行编译,在Terminal下运行: pio run -e dev -v 编译成功后,点击PlatformIO左上角的Project Task下面的dev ->Custom ->Prepare Logic。 注意: Prepare Logic生产的文件属性是只读,最好修改一下文件属性。 Prepare成功后(如上图所示),会生成一个Logic_dir的目录,该目录下会有一个Quartus下的FPGA的工程agrv2k_103_64.qpf,工程名字就是VE的文件名。该工程下主要有3个文件: l agrv2k_103_64.v 这是根据VE自动生成的,主要是芯片对外用到的pin功能,对应芯片的顶层模块。这个文件用户不要修改。 l alta_sim.v 这个文件提供芯片的系统功能 l 用户定义的模块文件,这里是analog_ip.v。 此时系统自动生成的用户模块只是一个接口,没有任何功能,如上图所示。此时,你可以使用例程提供的ahb2apb.V 和 analog_ip.v替换进来。 至此整个工程建立完毕。 注意: AGRV2KLxx 在ALTERA 里没有对应的芯片,采用Cyclone IV的 EP4CE75F23C8来模拟,因此Quartus里需要安装Cyclone IV的器件库。 另外,注意Top-Level entity的选择: Assignments -> Settings, top level 改成top 如果出现模块无法加载的情况,可能是hierarchy变了,Assignments -> Design Partitions Window,把所有partition都删掉,再重新跑一下tcl一下。 二、 编译 第一步: 运行Quartus的tools->TCL Scripts,如下图所示。 运行成功后,就可以看到系统占用的资源。 这里面不用去管device 型号,借用了一下cyclone IV的一个型号而已。 后期如果工程不换目录的话,tcl执行一次就行了。之后如果管脚以及使用的IP没有改变的话,可以直接编译,不需要执行TCL。改设计在原Quartus工程里编译,然后supra也编译(tools-compile)一下,就行了。 这里最好在Quartus下也compile一下。 第二步:打开Supra软件,注意版本是否为最新。 运行过setup.py的话,在AgRV_pio的目录下有Supra的快捷键。 运行Supra,在File -> Project -> Open Project 工程就在Logic_dir目录下。 打开工程后,运行Tools -> Compile

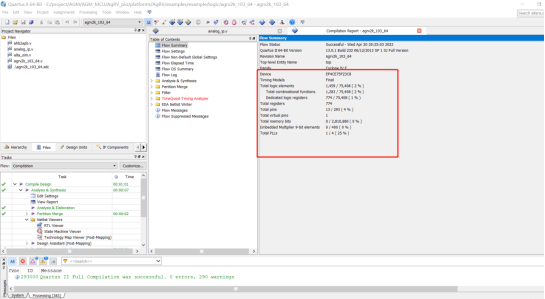

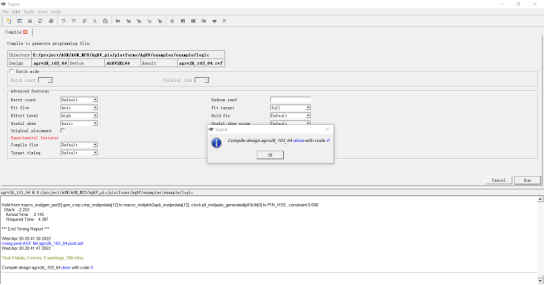

编译成功后,如下图:

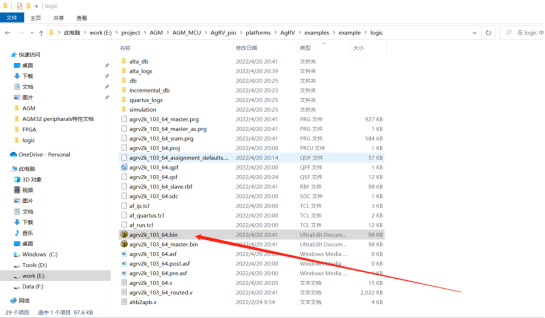

编译成功后在Logic_dir目录下会产生可供烧录的bin文件。

具体用户可以参见《MANUAL_Supra_6.2.pdf》。 三、 参考代码 参考Quartus的Hierarchy,这样便于理解代码。

Mcu访问FPGA的逻辑模块是通过AHB-APB总线来访问的,地址范围为0x6000_0000~0x7FFF_FFFF。具体这些地址如何来划分,是由FPGA代码决定的。参考例程里没有对高端地址(高16位)进行区分,只用了低16来区分ADC,DAC, CMP。地址分别如下: #define ADC0 ((ADC_TypeDef *) 0x60000000) #define ADC1 ((ADC_TypeDef *) 0x60001000) #define ADC2 ((ADC_TypeDef *) 0x60002000) #define DAC0 ((DAC_TypeDef *) 0x60003000) #define DAC1 ((DAC_TypeDef *) 0x60004000) #define CMP0 ((CMP_TypeDef *) 0x60005000) 也就是说用bit12~bit15来定义不同设备的地址空间。 四、 程序下载 AGRV2K(CPLD)烧写须知 |