|

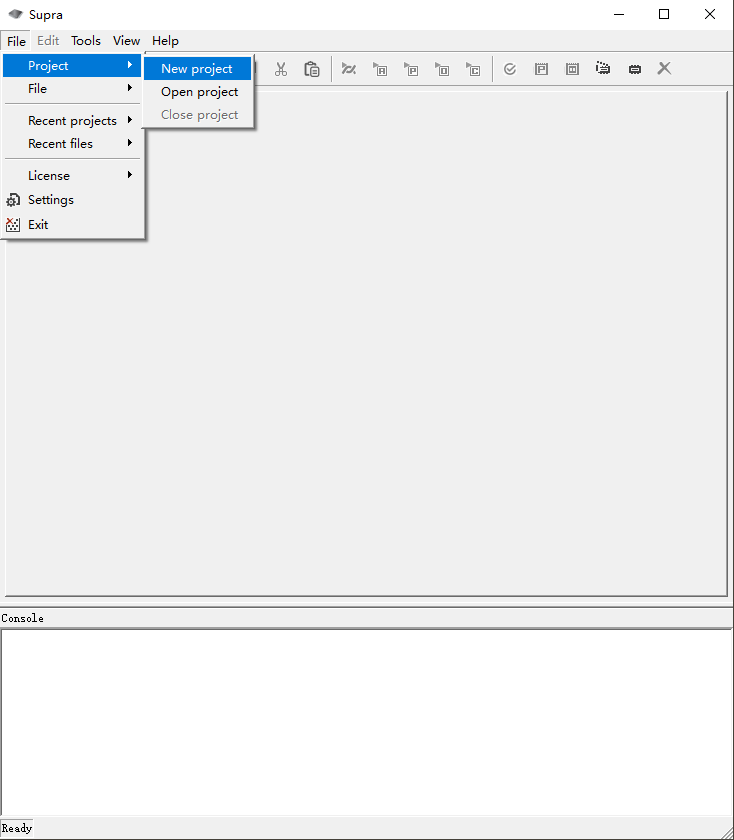

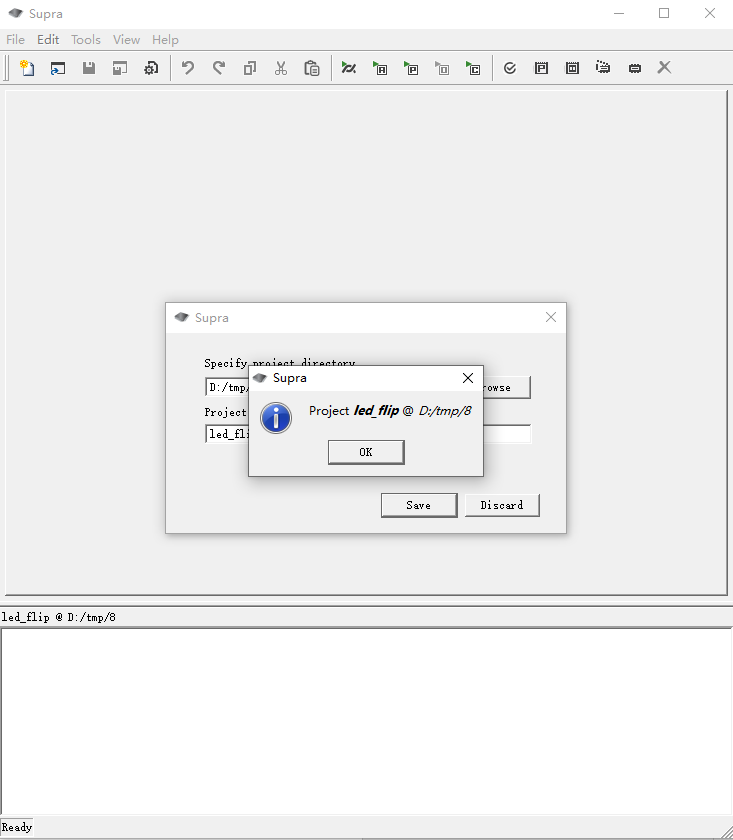

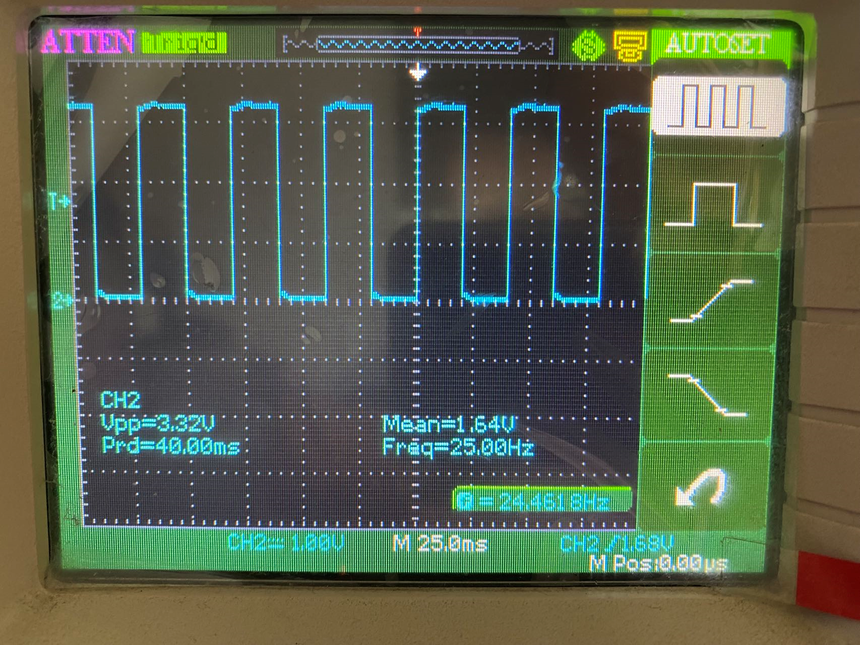

AGM AG1280Q48 开发流程(官方版)1. 环境 操作系统: Windows 10 软 件: Intel: Quartus II AGM: supra 测试硬件: AG1280Q48最小系统板 l 以工程【led_flip】为例阐述步骤,IO周期25Hz变化 AG1280Q48 可用IO为27个,其中1个IO需要连晶振,其余实际可用26个IO AG1280Q32 可用IO为13个,其中1个IO需要连晶振,其余实际可用12个IO 2. 步骤 1) Supra新建工程

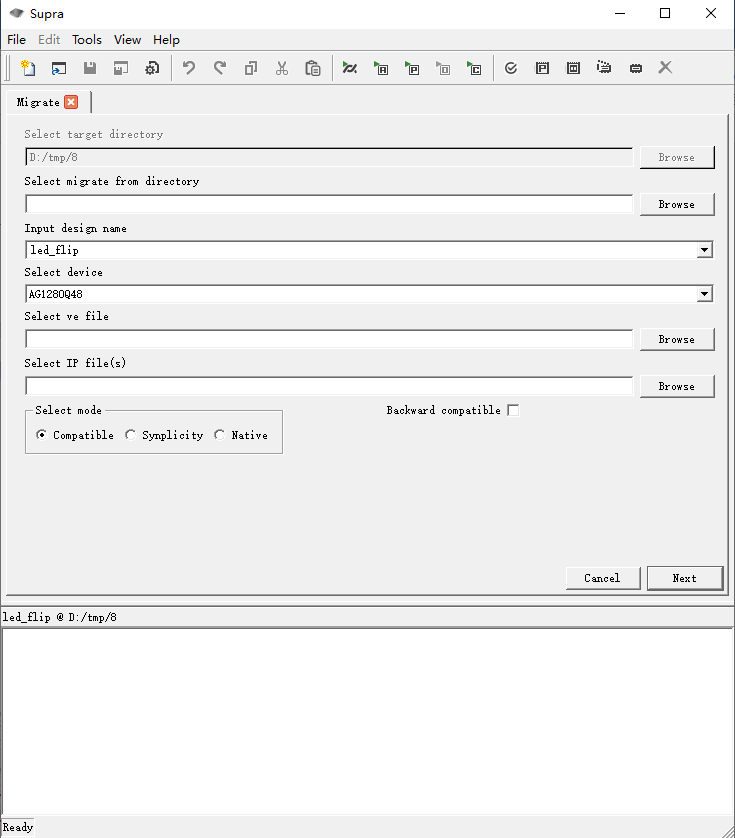

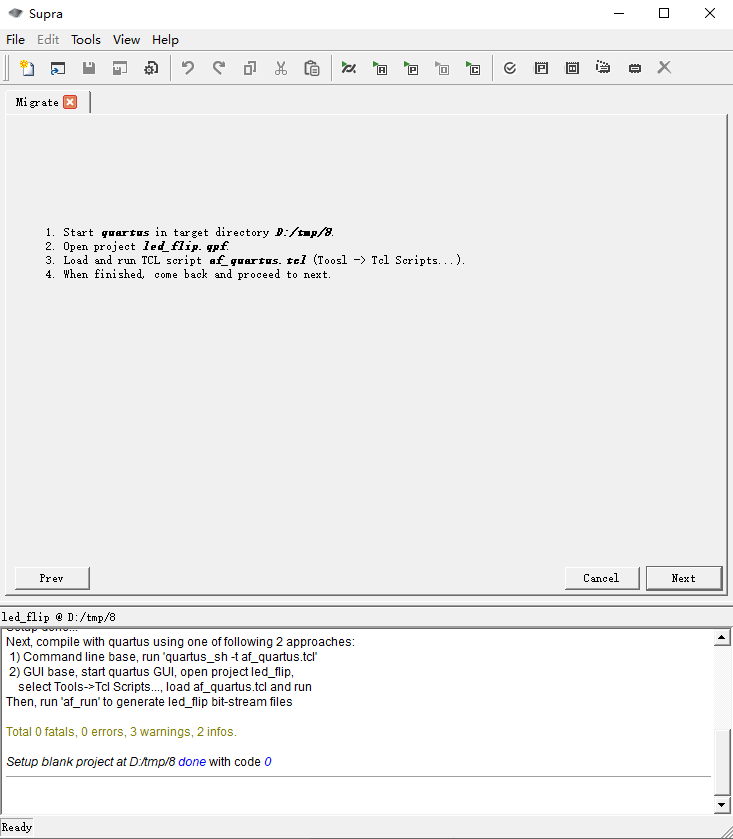

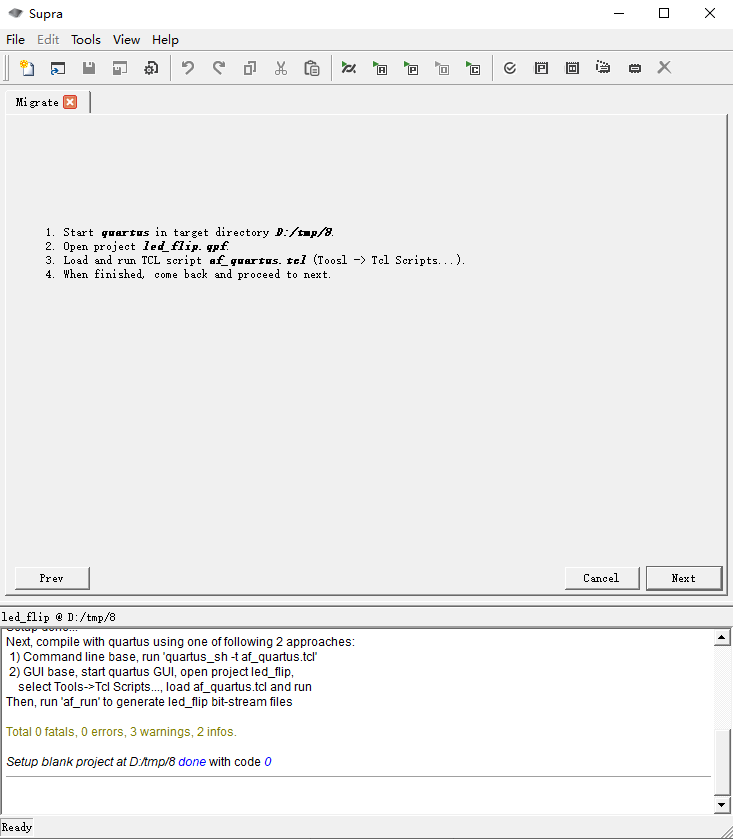

2) Supra点击【Tools】-【Migrate】 n 手动输入【Input design name】 n 下拉选择器件【AG1280Q48】 n 点击【next】

n 不点击【next】,也不用关闭Supra

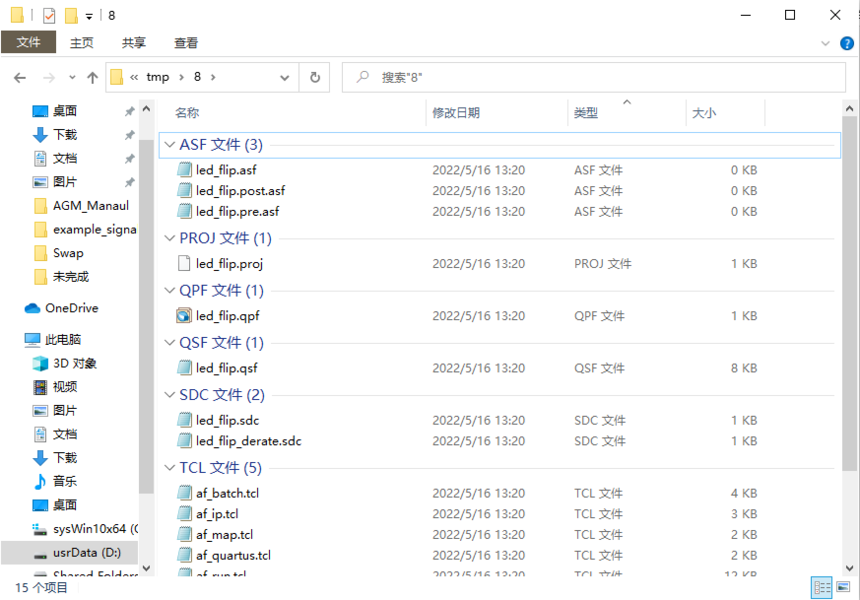

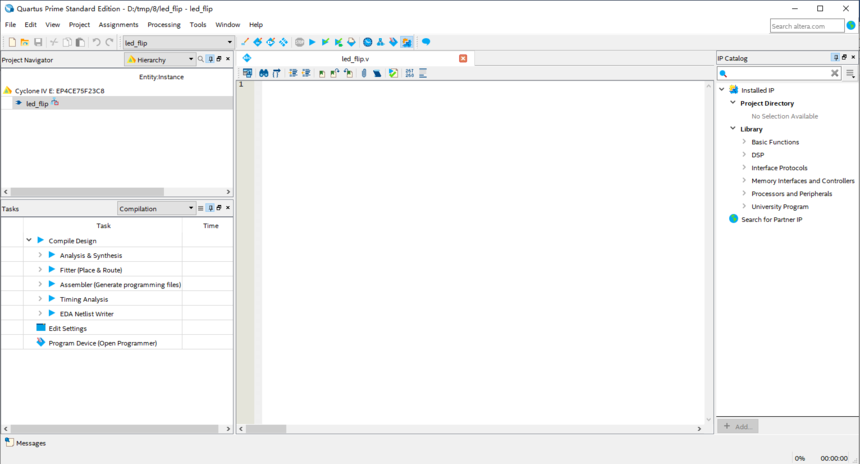

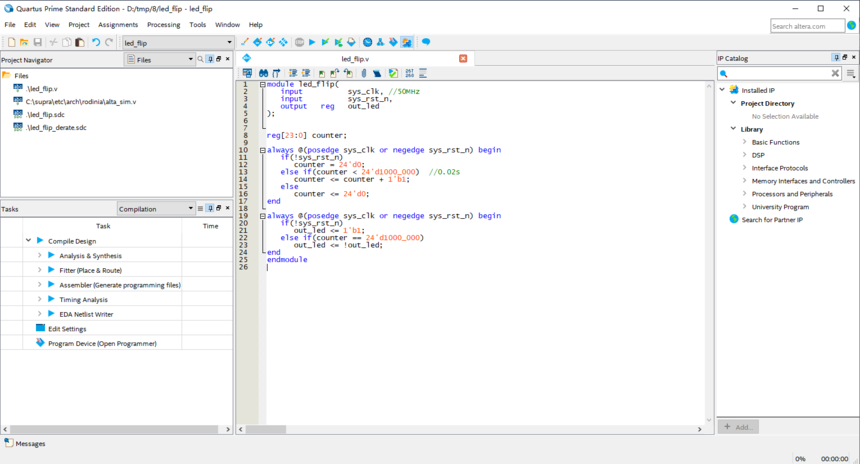

3) Quartus打开Supra新建目录下【*.qpf】文件 n Supra生成的【*.qpf】已经设置器件与基本参数,如下图所示 n 此处以【led_flip】为例阐述,编辑程序并保存

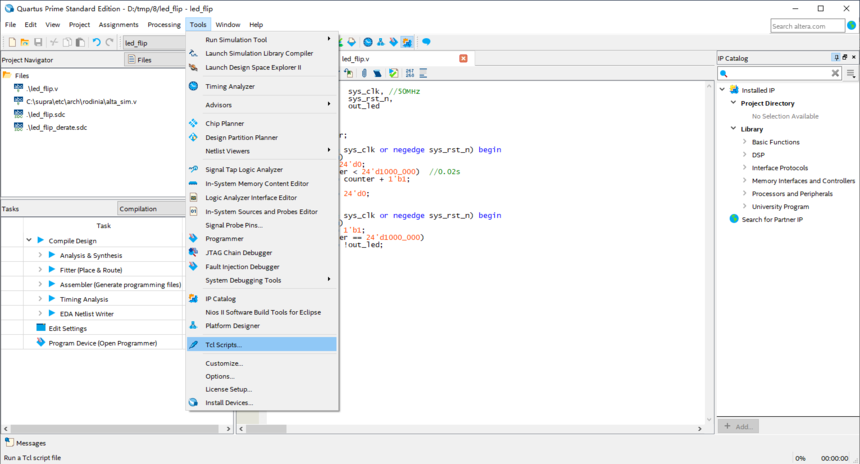

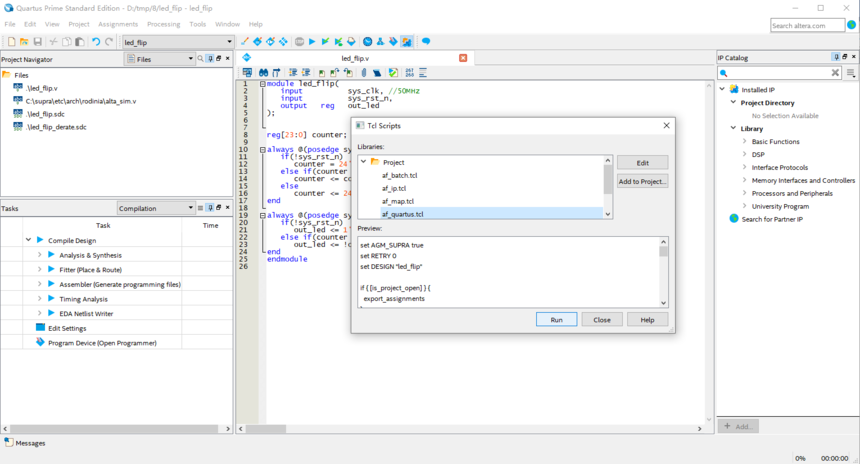

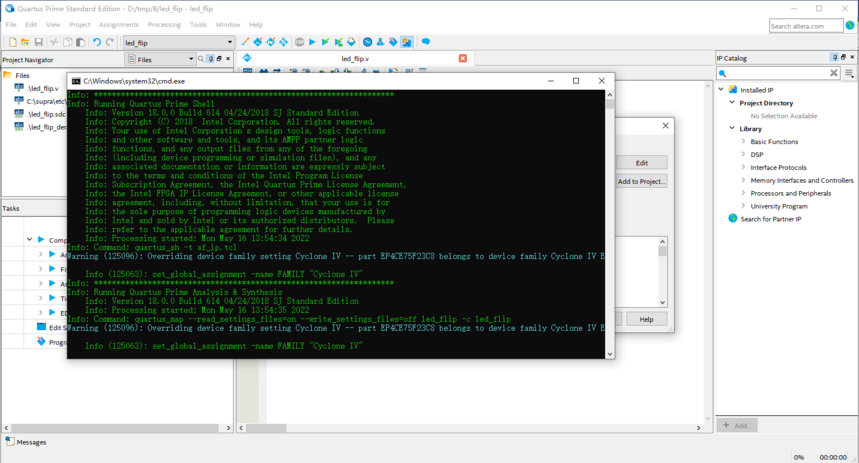

4) 运行【af_quartus.tcl】 n 点击【Tools】-【Tcl Scripts】 选中【af_quartus.tcl】,点击【run】 n 跳出命令框执行编译中…

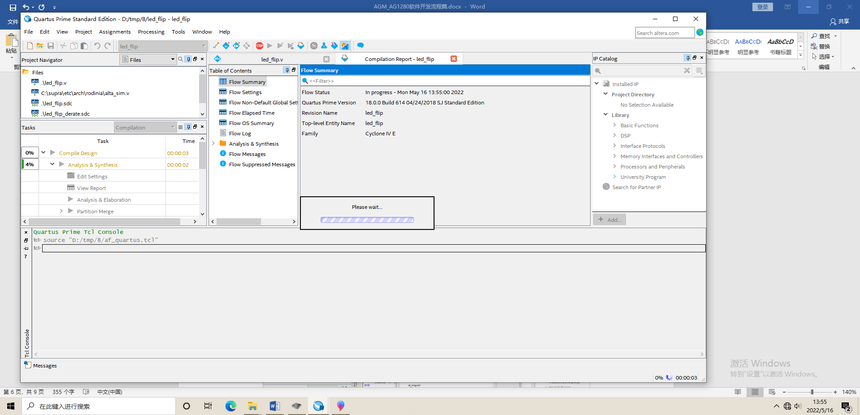

n 命令框关闭后,Quartus自动进入全编译…

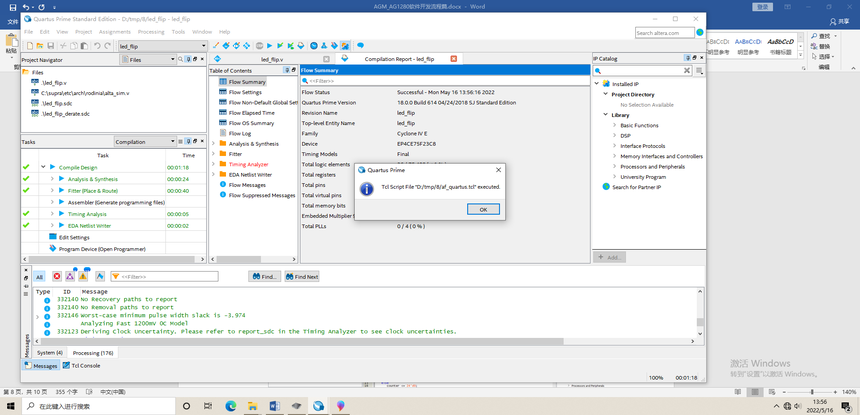

n Quartus全编译完成

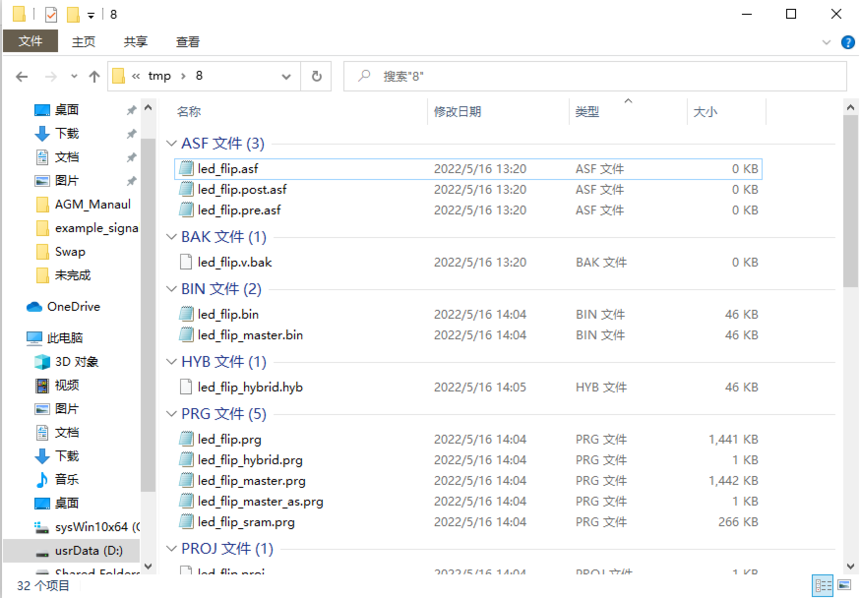

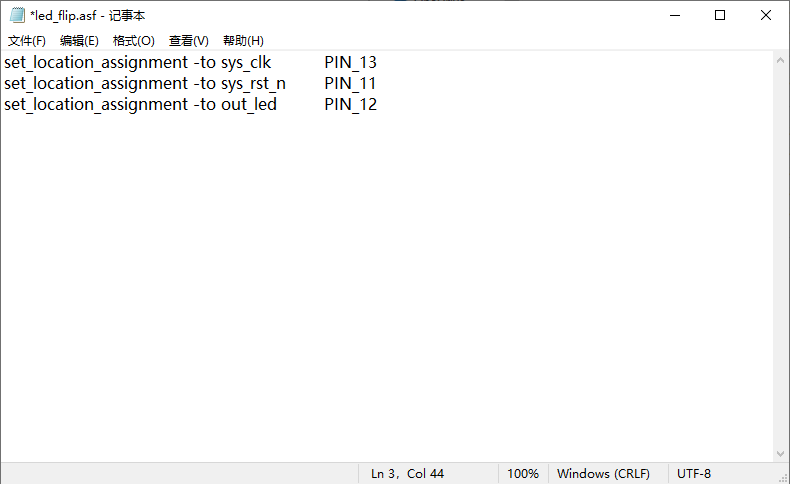

5) 编辑引脚配置 n 编辑【*.asf】文件 n 编辑IO标准,位置等设置信息(*格式可参考quartus *.qsf文件),如下 set_location_assignment -to sys_clk PIN_13 set_location_assignment -to sys_rst_n PIN_11 set_location_assignment -to out_led PIN_12

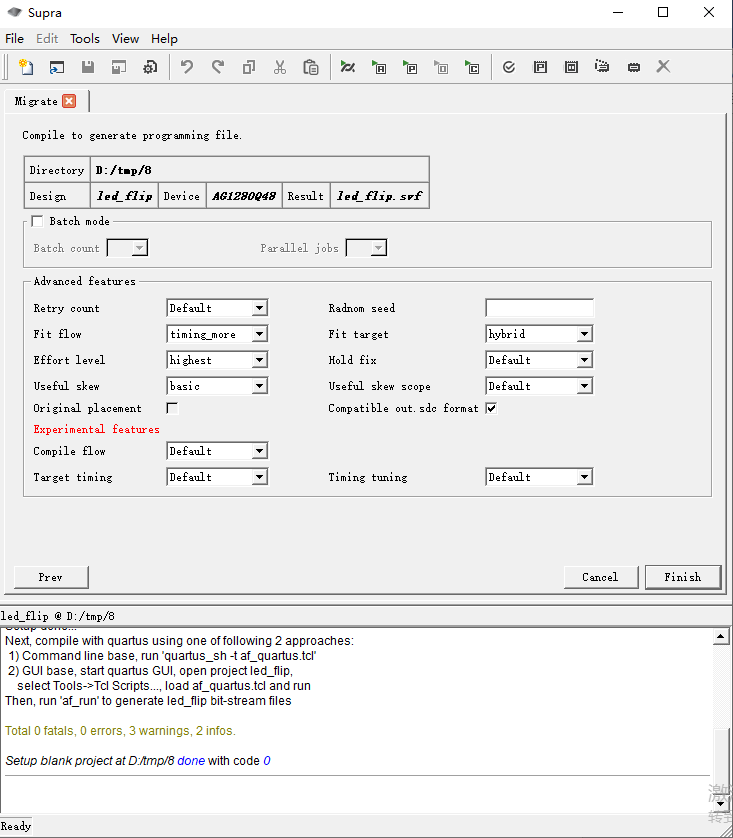

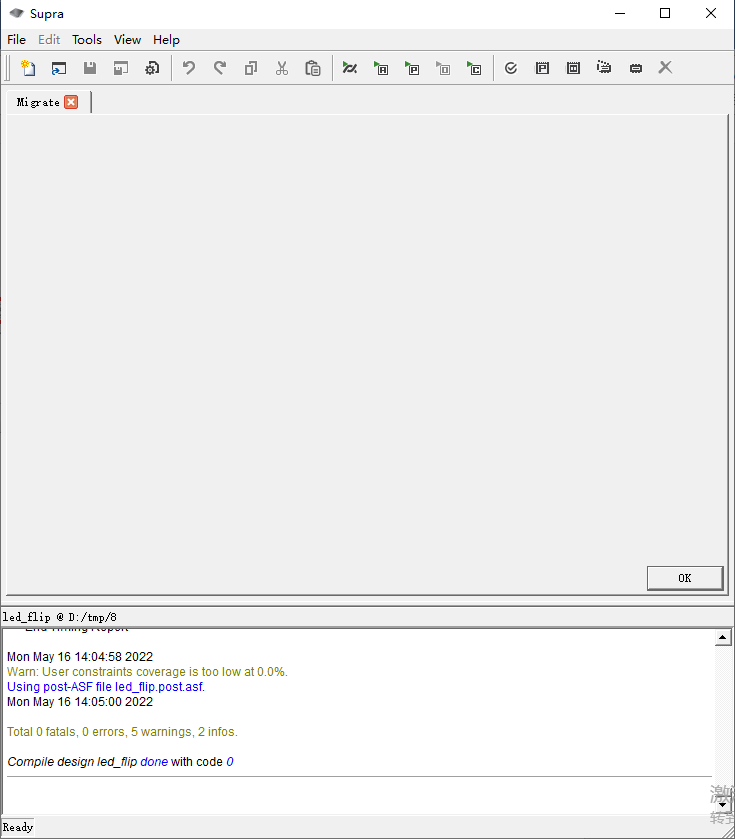

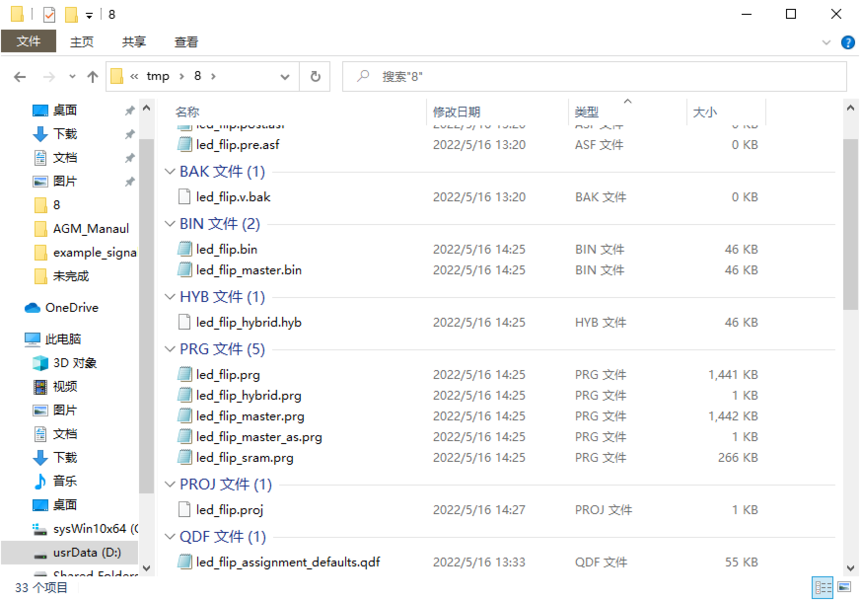

6) 继续步骤2)中Supra的步骤 n 点击【next】 n 点击【finish】 n 编译完成无报错,点击【OK】

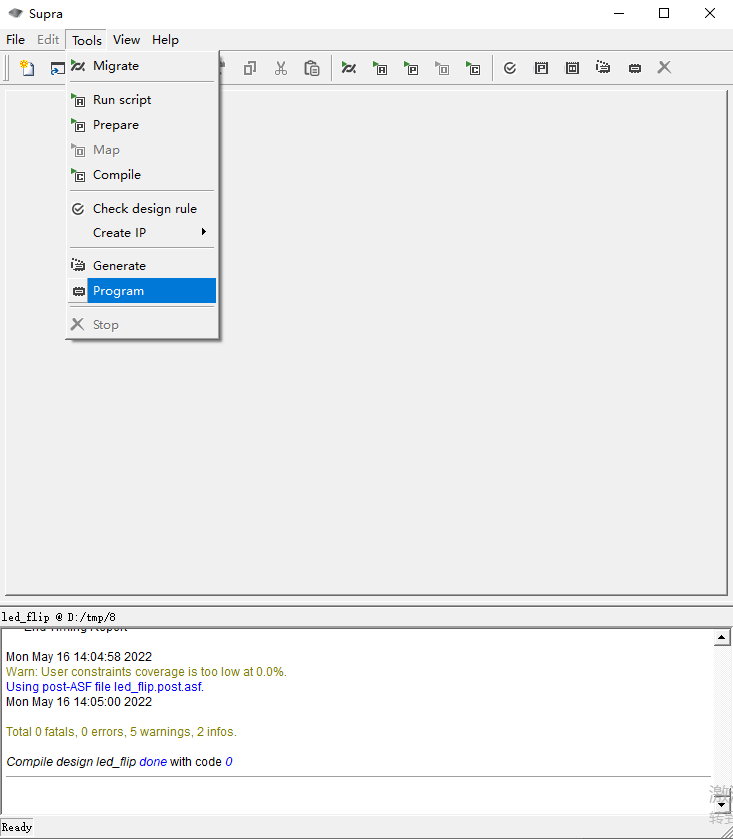

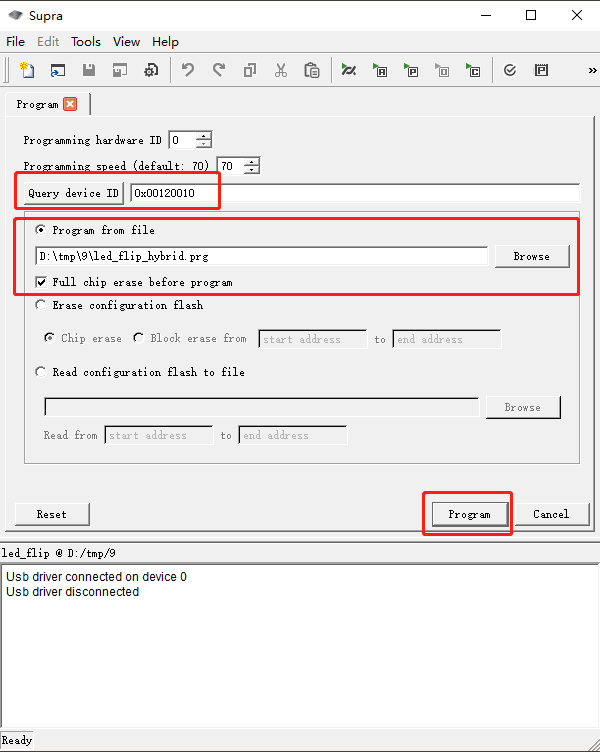

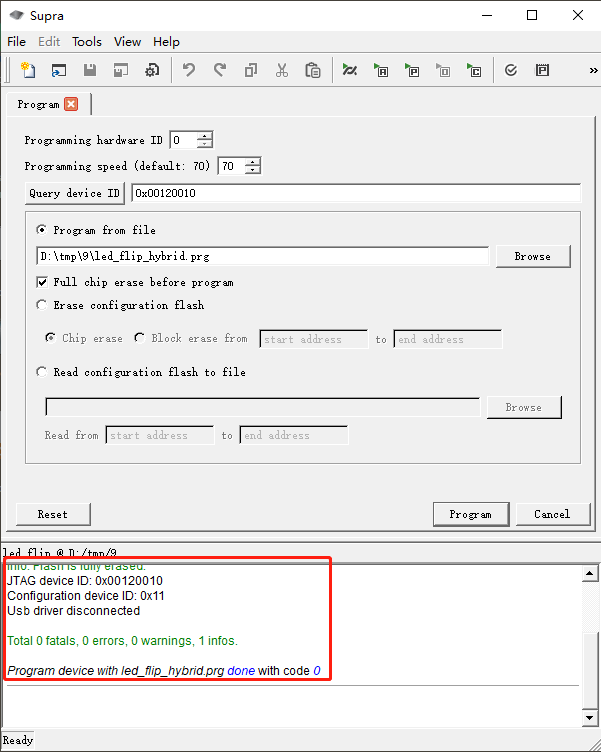

7) Supra下载 n 点击【Tools】-【Program】 n 点击Query device id 反馈正确ID n 选择【*_hybrid.prg】文件 n 勾选【full chip erase before program】 n 点击【program】

DEOM下载

|