|

AG10KL144H 升级使用 16K LEs 操作流程(AG16KL144A)AG10KL144H 转换注意事项 AG10KL144H 为 AG10KL144 升级型号,封装管脚兼容,性能更优,增加部分功能特性。 内部 IP 与 AG16K 一致。 芯片丝印:根据不同批次,有 2 种,均为正确标识: 1. 型号标识为 AG10KL144H 2. 日期编码(DATE CODE)后加 H,如 2302H,型号标识仍为 AG10KL144 原 AG10KL144 设计替换为 144H,需要注意以下事项。 1. Supra 原工程需要重新编译,Device 选择 AG10KL144H,其它设置可以不变。 2. AG10KL144 PLL 的复位控制可以省去,如已加入也可正常使用。 (参考上节 1.PLL) 3. AS 口烧写 FLASH 用 XXX_master_as.prg 文件,SPI 端口不需串接电阻。 (参考上节 5. AS 口在线烧写 FLASH) 4. PS 烧写可以支持数据文件的压缩。 (参考上节 10. 烧写文件压缩) 5. 原 AG10KL144 的 Dual-Boot IP(alta_boot)需要用 Remote-Upgrade IP(alta_remote)替 代,功能更强大,具体可以参考 Manual_remote.pdf 文档。 6. 原 AG10KL144 的 MCU IP(alta_mcu)需要用(alta_mcu_m3)替代。 7. 如果原 AG10KL144 设计 MSEL[0..2]串接了电阻到 VCC 或 GND,请改为 0 欧或直连,否则 可能会导致 Supra 烧录 FLASH 错误。 (参考上节 15. MSEL 配置模式选择) 8. 新增支持 Quartus II 中的 Signal Tap 功能,编译烧录后可使用。 AG10KL144H 如何升级使用 16K LEs 操作流程 AG10KL144H 为 AG10KL144 管脚兼容型号, 但实际逻辑资源可以达到 16K LEs,也可使 用 AG16K IP 。如果仅用 10K,可以遵循原兼容型号设计转换流程(参考 Manual_supra.pdf), 即采用 Quartus 的 EP4CE10E22 工程来转换,只是 Supra 内型号选择 AG10KL144H。 如果希望用到 16K LEs ,需要采用非兼容型号的 prepare 设计流程, 类似 AG10K/16K SDE176 系列。Supra 里选择 AG16KL144A 这个新型号。 软件开发流程 (Compatible 模式) 先用 Quartus 基于 Cyclone IV EP4CE15F23 为基础完成原始设计。管脚位置分配可先清空。 新建一个文本格式的管脚分配文件, 命名为<design>.ve。编辑 ve 文件加入 FPGA 的 IO 位置设置, 这里需要参考 AG10KL144 的管脚位置,ve 文件格式如下(管脚设计名称+空格+ 封装管脚名称),例如:

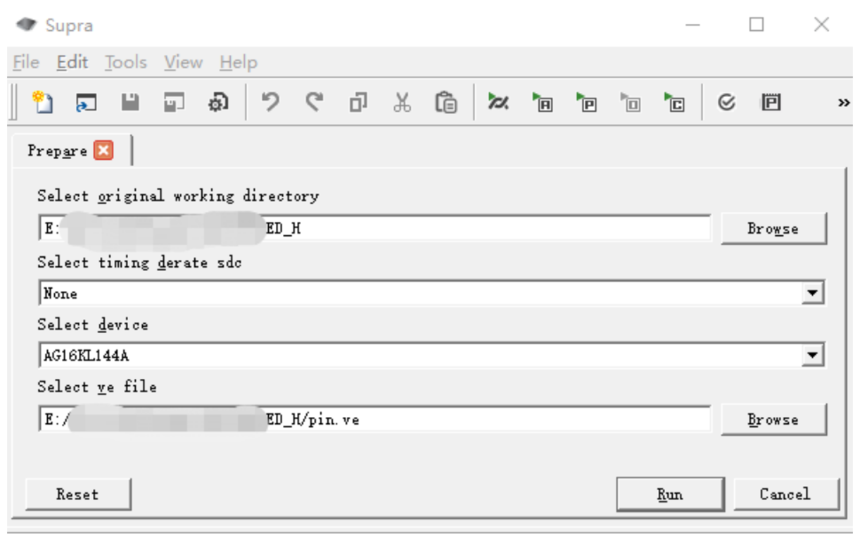

新建一空目录作为 AG16KL144A 的项目目录。打开 AGM Supra 软件,在此目录中新建工程。执行 Tools-Prepare。选择原 Quartus II 项目目录,Device 选 AG16KL144A,并选择编辑好的 ve 文件后,点击 Run。正确运行后会生成 af_prepare.tcl 等文件。

打开原 Quartus 项目,通过 Tools-Tcl Scripts 运行 af_prepare.tcl 脚本文件,会把 ve 的内容导入到 EP4CE15 对应的管脚分配,并继续执行编译过程,在项目目录中生成 Simulation 目录以及综合后的 vo 等文件。 打开 AGM Supra 软件,执行 Tools-Migrate。Target directory 默认为当前工程目录,From directory 为原 EP4CE15 的工程目录。Input design name,可以从下拉框中直接选取。Device为 AG16KL144A,同样选择 ve 文件。

点击 Next,参考页面说明 OR 上面的部分(确认前面已运行过 af_prepare.tcl)即直接点击 Next。

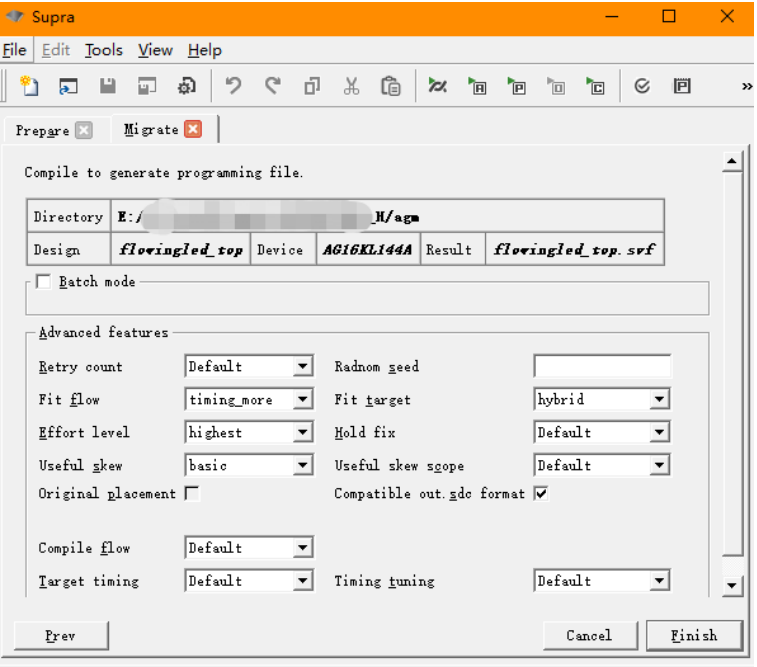

下面进入编译界面中,可设置编译参数,或直接采用默认设置。

点击 Finish,进入编译过程,在 Console 窗口可查看编译信息 log。成功编译后,即生成 配置烧写文件。 提示:如需继续修改原设计代码(不改变管脚),由于 af_prepare.tcl 已把管脚设置好, 可直接在原 Quartus 工程中修改代码并完全编译。然后在 Supra 中执行 Tools-Compile,即上 面最后一步界面,点击 Run 完成最终编译。 特别提醒:需要下载最新版本的supra |