|

AG1280"锁死"问题及解决方法AG1280"锁死"问题及解决方法

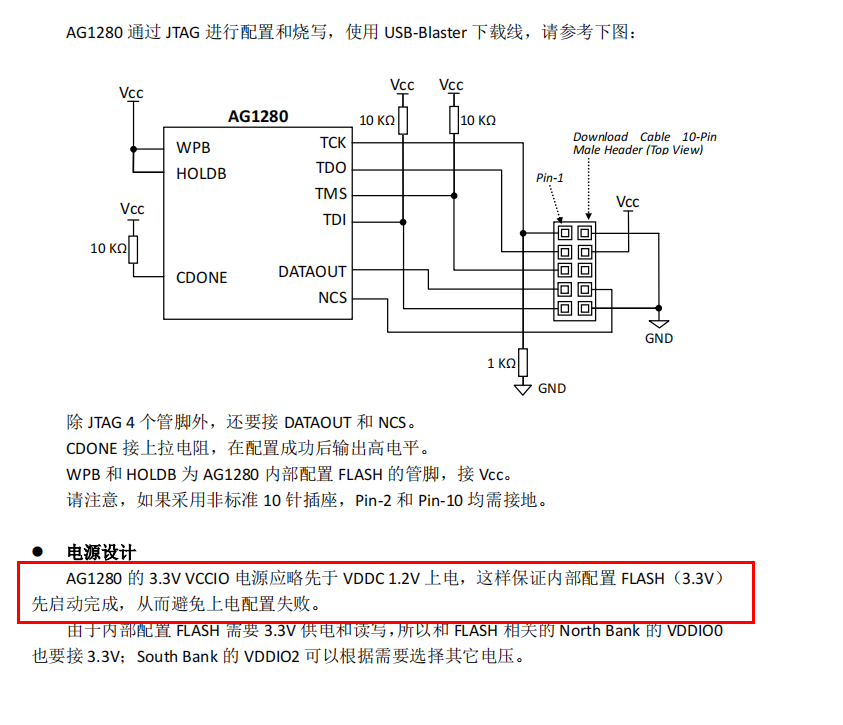

故障表现和排查方法 某天遇到一颗"锁死"的AG1280Q48芯片,具体故障是JTAG不通,板子上电电流大约3mA,然而连接USB-Blaster下载以后电流飙升到51mA。实测JTAG接口的几个信号,发现只有TDI不太正常,连接USB-Blaster时TDI管脚是2.0V,数字IO信号,要么是0V,要么是3.3V。2.0V这个电压显然是不正常的。感觉是USB-Blaster在努力将TDI管脚拉低,但是芯片内部有一股神奇的力量将TDI管脚拉高,最终就僵持在2.0V电压上了。试着拔掉USB-Blaser,直接把TDI管脚直接接到GND然后上电,板子电流依然会从3mA增加到51mA,然而不带电测试TDI到3.3V有8.4k左右电阻,和其它正常板子一样,感觉芯片应该没有坏。 因和解决方案 AG1280内部使用了JTAG接口的管脚,或者说有其它的IO和JTAG管脚接在一起,如果用户设计文件有未约束的管脚,有可能会自动分配到和JTAG管脚连接的IO上,导致JTAG接口通讯异常,我这里遇到的问题是和TDI管脚连接的内部IO设置为了输出,影响了TDI管脚上的JTAG测试数据输入。解决方法也很简单:擦除内部配置闪存即可。然而内部闪存通过JTAG接口烧录,现在JTAG接口无法通讯,如何擦除内部闪存呢? 原厂的文档中提到过:AG1280 的3.3V VCCIO 电源应略先于VDDC 1.2V上电,这样保证内部配置 FLASH(3.3V)先启动完成,从而避免上电配置失败。

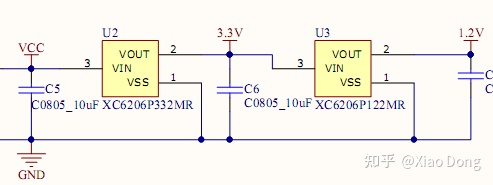

现在我们希望上电配置失败不加载配置闪存中的数据,那么可以将上电时序反过来,让1.2V先于3.3V上电,FPGA核心启动以后,擦除配置闪存就可以了。上图的电路中,修改两个LDO的硬件很麻烦,我们换个思路,利用LDO输出饱和特性,使用一台可调电源即可做出需要的上电时序,步骤如下:

这个问题出现概率很低,一方面是因为用户的误操作,另外一方面是因为官方的Supra软件在布局布线时将未使用的IO放到了JTAG相关管脚上,Supra在布局布线时增加一个检查就可以避免了。在厂家修改软件之前,作为用户,设计中使用的IO都做好约束,不要让Supra自动分配管脚即可。 类似的问题在MCU上也很常见,比如用户代码中无意中修改了SWDIO和SWCLK两个管脚的默认配置,关闭了SWD调试接口,然后xxLink调试器就连不上了,很多客户此时就开始抱怨xxLink调试器有问题...其实只要改一下MCU引导模式后重启进入芯片内置的bootloader,擦除用户固件就可以了。 |