|

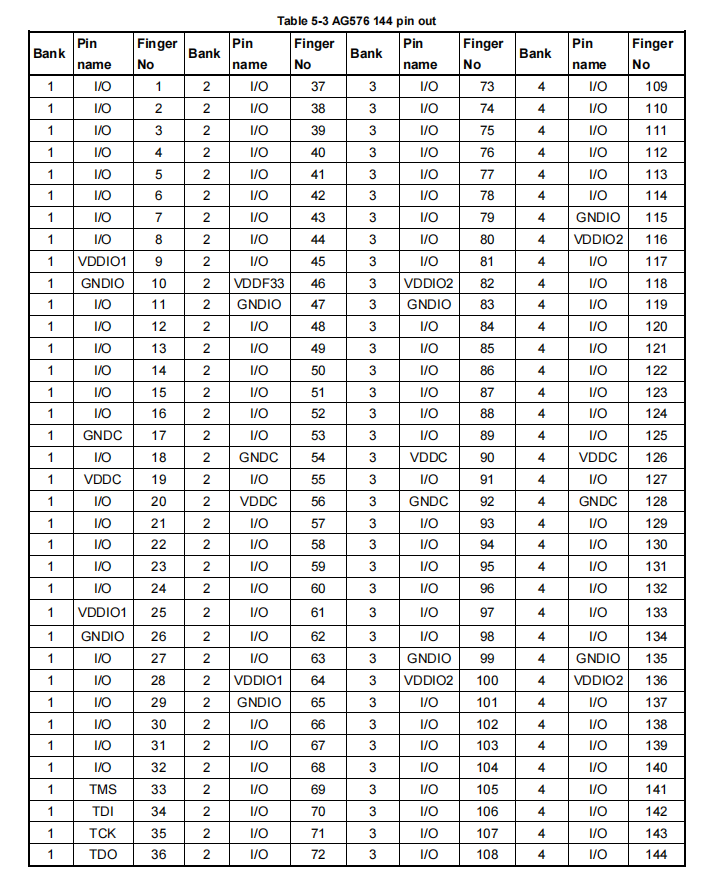

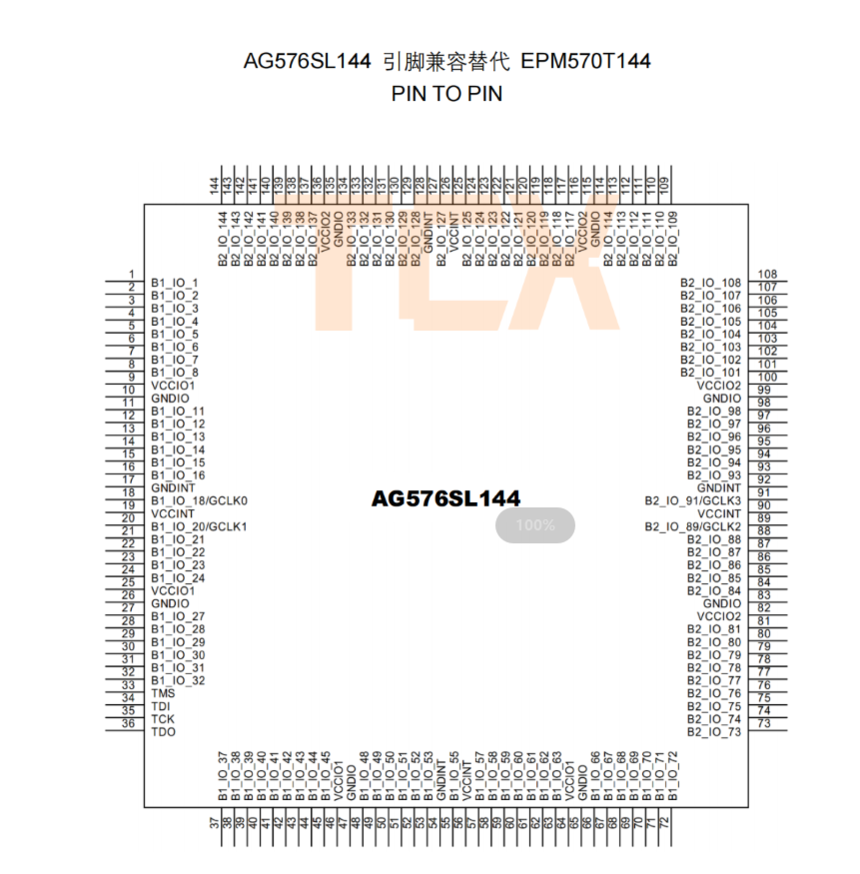

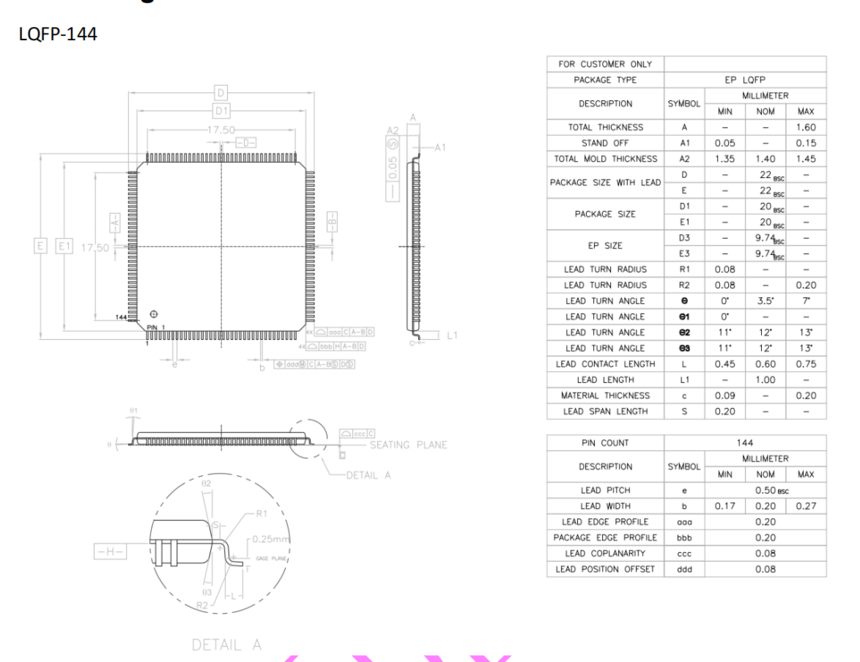

AG576SL144AG576 CPLDs is the low cost CPLDs. This instant-on, non-volatile CPLD family targets general-purpose and low-density logic. The logic density is 576 Logic Elements with LQFP-100 and 144 package. • Low-Cost and low-power CPLD • Instant-on, non-volatile standard compatible architecture. • Up to 4 global clock lines in the global clock network that drive throughout the entire device. • Provides programmable fast propagation delay and clock-to-output times. • Provides PLL per device, clock multiplication, and phase shifting. • UFM supports non-volatile storage up to 256 Kbits. • Supports 3.3-V, 2.5-V, 1.8-V, and 1.5-V logic level • Programmable slew rate, drive strength, bus-hold, programmable pull-up resistors, open-drain output, Schmitt triggers and programmable input delay. Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry complaint with IEEE Std. 1149.1-1990 • ISP circuitry compliant with IEEE Std. 1532 • 3.3-V, 2.5-V, 1.8-V, 1.5-V LVCMOS and LVTTL standards • Emulated LVDS output (LVDS_E_3R) • Emulated RSDS output (RSDS_E_3R) AG576 cpld是一种低成本的cpld。这种即时启动、非易失性CPLD家族的目标是通用和低密度逻辑。逻辑密度为576 logic Elements, LQFP-100和144封装。 • 低成本和低功耗CPLD • 即时启动,非易失性标准兼容架构。 • 全局时钟网络中多达4条全局时钟线,驱动整个设备。 • 提供可编程的快速传播延迟和时钟到输出时间。 • 提供每个设备的锁相环PLL,时钟乘法和相移。 • UFM支持高达256kbits的非易失性存储。 • 支持3.3 v、2.5 v、1.8 v、1.5 v逻辑电平 • 可编程转换速率,驱动强度,总线保持,可编程上拉电阻,开漏输出,施密特触发器和可编程输入延迟。 • 内置JTAG 和BST,电路符合 IEEE 标准。 1149.1-1990 • ISP电路符合IEEE标准1532 • 3.3 v, 2.5 v, 1.8 v, 1.5 v LVCMOS和LVTTL标准 • 仿真LVDS输出(LVDS_E_3R) • 模拟RSDS_E_3R输出 • 工作结温范围为 -40 至 100 °C

上一篇AG576SL100下一篇AG16KF256 |