|

AG16KL144AAG16K FPGA devices are targeted to high-volume, cost-sensitive, applications, enabling system designers to meet increasing performance requirements while lowering costs. The device AG16K offers supreme quality, stability, and exceptional pricing value. Features

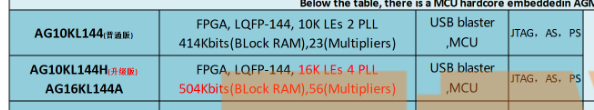

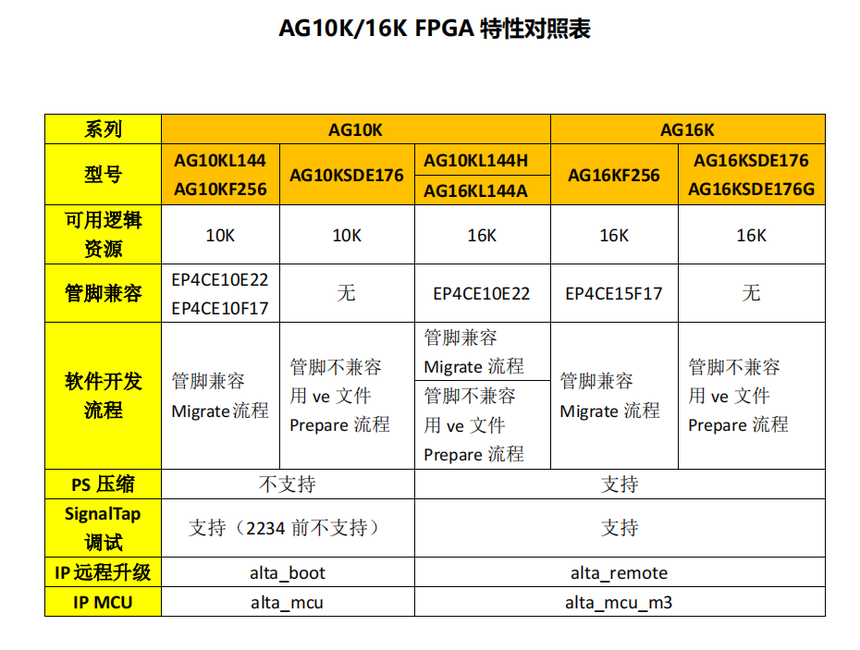

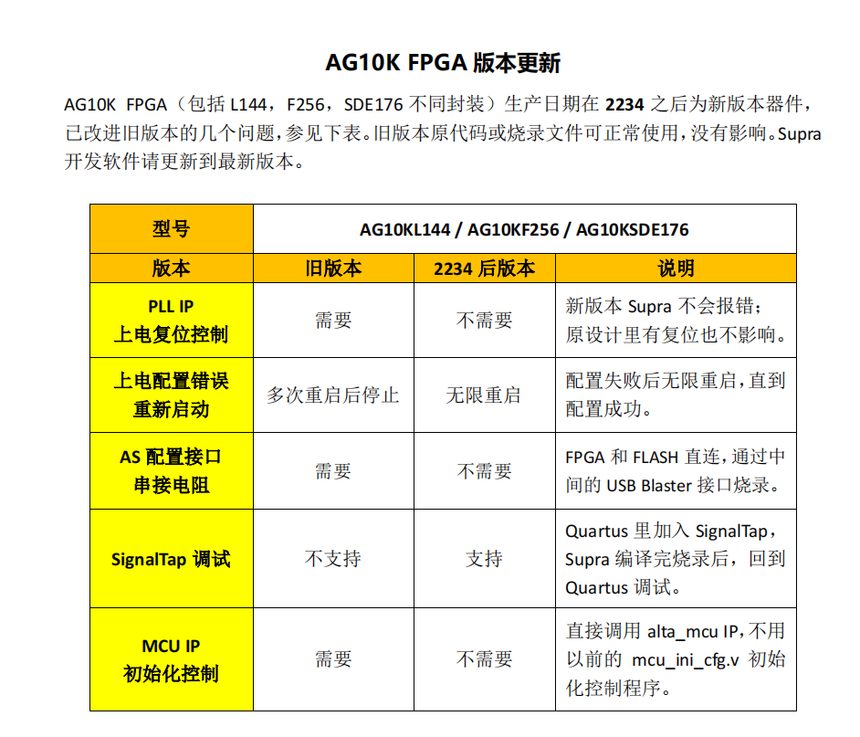

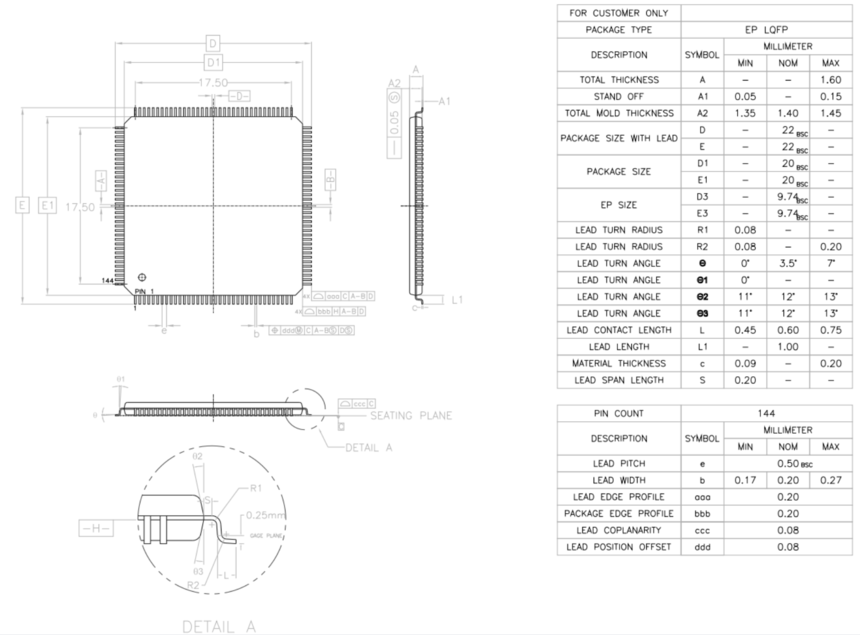

AG16KL144A is compatible with AG10KL144. AG16KЃЈAG16KL144AЃЉ FPGAЦїМўеыЖдДѓШнСПЁЂГЩБОУєИаЕФгІгУЃЌЪЙЯЕЭГЩшМЦШЫдБФмЙЛдкНЕЕЭГЩБОЕФЭЌЪБТњзуШевцдіГЄЕФадФмвЊЧѓЁЃЩшБИAG16KЬсЙЉСЫзюИпЕФжЪСПЃЌЮШЖЈадКЭзПдНЕФЖЈМлМлжЕЁЃ • ИпУмЖШМмЙЙЃЌ16K LEs • ИпДя504KbitsЕФRAMПеМф • ЖрДя56Иі18 x 18ЮЛЧЖШыЪНГЫЪ§ЦїЃЌУПИіЖМПЩХфжУЮЊСНИіЖРСЂЕФ9 x 9ЮЛГЫЪ§Цї • УПИіЩшБИЬсЙЉ4ИіЫјЯрЛЗЃЈPLLЃЉЃЌЬсЙЉЪБжгГЫЗЈКЭЯрвЦ • ИпЫйВюЗжI/OБъзМжЇГжЃЌАќРЈLVDS, rsd, mini-LVDS, vpecl • SSTLЁЂSSTL- ii IOБъзМЃЌжЇГжDDRЁЂDDR2 • ЕЅЖЫI/OБъзМжЇГжЃЌАќРЈ3.3VЁЂ2.5VЁЂ1.8VЁЂ1.5V LVCMOSКЭLVTTL • ЭЈгУАќзАбЁЯюЃЌLQFP-144ЗтзА • 2Иі12ЮЛSarADC(ЧЖШыЪНЮТЖШДЋИаЦї) • ЭЈЙ§JTAGКЭSPIНгПкСщЛюХфжУЩшБИ • дЖГЬИќаТЃЌЭЈЙ§ЁАЫЋЦєЖЏЁБЪНЪЕЯж • жЇГжаОЦЌаХКХЕїЪд • ЙЄзїНсЮТЗЖЮЇЮЊ -40 жС 100 ЁуC

AG16KL144A ШчКЮЩ§МЖЪЙгУ 16K LEs AG16KL144A ЮЊ AG10KL144 ЙмНХМцШнаЭКХЃЌЕЋЪЕМЪТпМзЪдДПЩвдДяЕН 16K LEsЃЌвВПЩЪЙ гУ AG16K IPЁЃШчЙћНігУ 10KЃЌПЩвдзёбдМцШнаЭКХЩшМЦзЊЛЛСїГЬЃЈВЮПМ Manual_supra.pdfЃЉЃЌ МДВЩгУ Quartus ЕФ EP4CE10E22 ЙЄГЬРДзЊЛЛЃЌжЛЪЧ Supra ФкаЭКХбЁдё AG10KL144HЁЃ ШчЙћЯЃЭћгУЕН 16K LEsЃЌашвЊВЩгУЗЧМцШнаЭКХЕФ prepare ЩшМЦСїГЬЃЌРрЫЦ AG10K/16K SDE176 ЯЕСаЁЃSupra РябЁдё AG16KL144A етИіаТаЭКХЁЃ ШэМўПЊЗЂСїГЬЃЈCompatible ФЃЪНЃЉ ЯШгУ Quartus Лљгк Cyclone IV EP4CE15F23 ЮЊЛљДЁЭъГЩдЪМЩшМЦЁЃЙмНХЮЛжУЗжХфПЩЯШЧхПеЁЃ аТНЈвЛИіЮФБОИёЪНЕФЙмНХЗжХфЮФМўЃЌУќУћЮЊ<design>.veЁЃБрМ ve ЮФМўМгШы FPGA ЕФ IO ЮЛжУЩшжУЃЌетРяашвЊВЮПМ AG10KL144 ЕФЙмНХЮЛжУЃЌve ЮФМўИёЪНШчЯТЃЈЙмНХЩшМЦУћГЦ+ПеИё+ ЗтзАЙмНХУћГЦЃЉЃЌР§ШчЃК

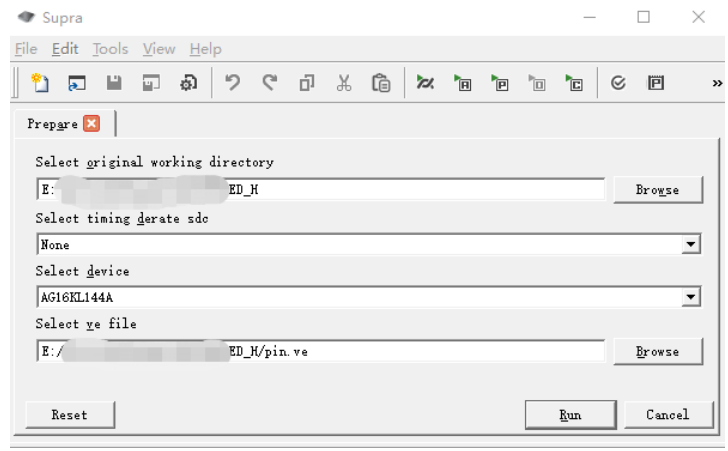

аТНЈвЛПеФПТМзїЮЊ AG16KL144A ЕФЯюФПФПТМЁЃДђПЊ AGM Supra ШэМўЃЌдкДЫФПТМжааТНЈЙЄ ГЬЁЃжДаа Tools-PrepareЁЃбЁдёд Quartus II ЯюФПФПТМЃЌDevice бЁ AG16KL144AЃЌВЂбЁдёБрМКУ ЕФ ve ЮФМўКѓЃЌЕуЛї RunЁЃе§ШЗдЫааКѓЛсЩњГЩ af_prepare.tcl ЕШЮФМўЁЃ

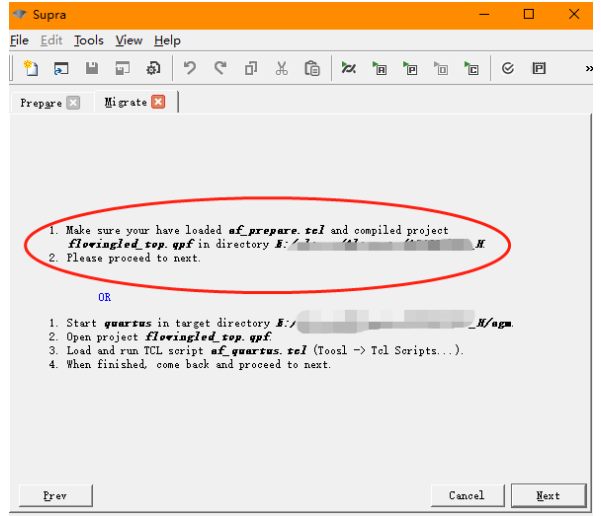

ДђПЊд Quartus ЯюФПЃЌЭЈЙ§ Tools-Tcl Scripts дЫаа af_prepare.tcl НХБОЮФМўЃЌЛсАб ve ЕФФк ШнЕМШыЕН EP4CE15 ЖдгІЕФЙмНХЗжХфЃЌВЂМЬајжДааБрвыЙ§ГЬЃЌдкЯюФПФПТМжаЩњГЩ Simulation ФП ТМвдМАзлКЯКѓЕФ vo ЕШЮФМўЁЃ ДђПЊ AGM Supra ШэМўЃЌжДаа Tools-MigrateЁЃTarget directory ФЌШЯЮЊЕБЧАЙЄГЬФПТМЃЌFrom directory ЮЊд EP4CE15 ЕФЙЄГЬФПТМЁЃInput design nameЃЌПЩвдДгЯТРПђжажБНгбЁШЁЁЃDevice ЮЊ AG16KL144AЃЌЭЌбљбЁдё ve ЮФМўЁЃ

ЕуЛї NextЃЌВЮПМвГУцЫЕУї OR ЩЯУцЕФВПЗжЃЈШЗШЯЧАУцвбдЫааЙ§ af_prepare.tclЃЉМДжБНгЕу Лї NextЁЃ

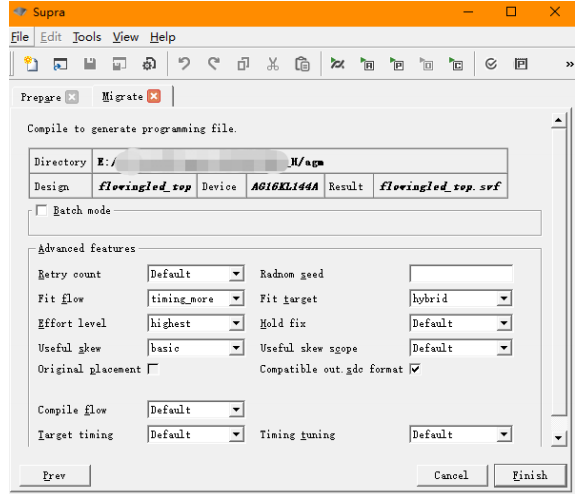

ЯТУцНјШыБрвыНчУцжаЃЌПЩЩшжУБрвыВЮЪ§ЃЌЛђжБНгВЩгУФЌШЯЩшжУЁЃ

ЕуЛї FinishЃЌНјШыБрвыЙ§ГЬЃЌдк Console ДАПкПЩВщПДБрвыаХЯЂ logЁЃГЩЙІБрвыКѓЃЌМДЩњГЩ ХфжУЩеаДЮФМўЁЃ ЬсЪОЃКШчашМЬајаоИФдЩшМЦДњТыЃЈВЛИФБфЙмНХЃЉЃЌгЩгк af_prepare.tcl вбАбЙмНХЩшжУКУЃЌ ПЩжБНгдкд Quartus ЙЄГЬжааоИФДњТыВЂЭъШЋБрвыЁЃШЛКѓдк Supra жажДаа Tools-CompileЃЌМДЩЯ УцзюКѓвЛВННчУцЃЌЕуЛї Run ЭъГЩзюжеБрвыЁЃ

ашвЊЛёШЁИќЖрЕФЁАзЪСЯЁБКЭЁАжЇГжЁБКЭЁАбљЦЌВтбљЩъЧыЁБПЩвдСЊЯЕЮвУЧ ЬсЙЉЁАаОЦЌВтбљ-ЗЂЫЭзЪСЯ-ММЪѕжЇГж-ХњСПВЩЙКЁБ СЊЯЕЗНЪНЃК вІЙЄ 13661545024ЃЈVXЭЌКХЃЉ (МгЕФЪБКђБИзЂЯТЙЋЫОУћКЭИіШЫУћзжЃЉ дкЯпЩЬГЧЃКagm-micro.taobao.com ЙЋЫОЭјеОЃКwww.agm-micro.com зЪСЯЭјеО: www.tcx-micro.com |