|

AGM 全新升级发布 AG10KL144H

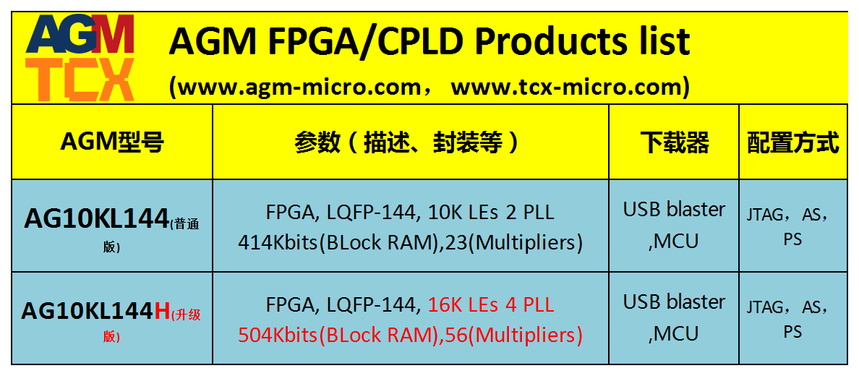

AGM 全新升级发布 AG10KL144H AG10KL144H 升级说明 AG10KL144H 为 AG10KL144 升级型号,封装管脚兼容,性能更优,增加部分功能特性。 芯片丝印:根据不同批次,有 3 种,均为正确标识。 1.型号标识丝印为 AG10KL144H; 2.日期编码 (DATE CODE) 后加 H,型号标识丝印仍为 AG10KL144; 3.日期编码 (DATE CODE) 后加 H,型号标识丝印为 AK10KL144。 型号标识仍为 AG10KL144 AG10KL144H 转换注意事项 AG10KL144H 为 AG10KL144 升级型号,封装管脚兼容,性能更优,增加部分功能特性。 内部 IP 与 AG16K 一致。 芯片丝印:根据不同批次,有 2 种,均为正确标识: 1. 型号标识为 AG10KL144H 2. 日期编码(DATE CODE)后加 H,如 2302H,型号标识仍为 AG10KL144 原 AG10KL144 设计替换为 144H,需要注意以下事项。 1. Supra 原工程需要重新编译,Device 选择 AG10KL144H,其它设置可以不变。 2. AG10KL144 PLL 的复位控制可以省去,如已加入也可正常使用。 (参考上节 1.PLL) 3. AS 口烧写 FLASH 用 XXX_master_as.prg 文件,SPI 端口不需串接电阻。 (参考上节 5. AS 口在线烧写 FLASH) 4. PS 烧写可以支持数据文件的压缩。 (参考上节 10. 烧写文件压缩) 5. 原 AG10KL144 的 Dual-Boot IP(alta_boot)需要用 Remote-Upgrade IP(alta_remote)替 代,功能更强大,具体可以参考 Manual_remote.pdf 文档。 6. 原 AG10KL144 的 MCU IP(alta_mcu)需要用(alta_mcu_m3)替代。 7. 如果原 AG10KL144 设计 MSEL[0..2]串接了电阻到 VCC 或 GND,请改为 0 欧或直连,否则 可能会导致 Supra 烧录 FLASH 错误。 (参考上节 15. MSEL 配置模式选择) 8. 新增支持 Quartus II 中的 Signal Tap 功能,编译烧录后可使

|