|

AG576SL100

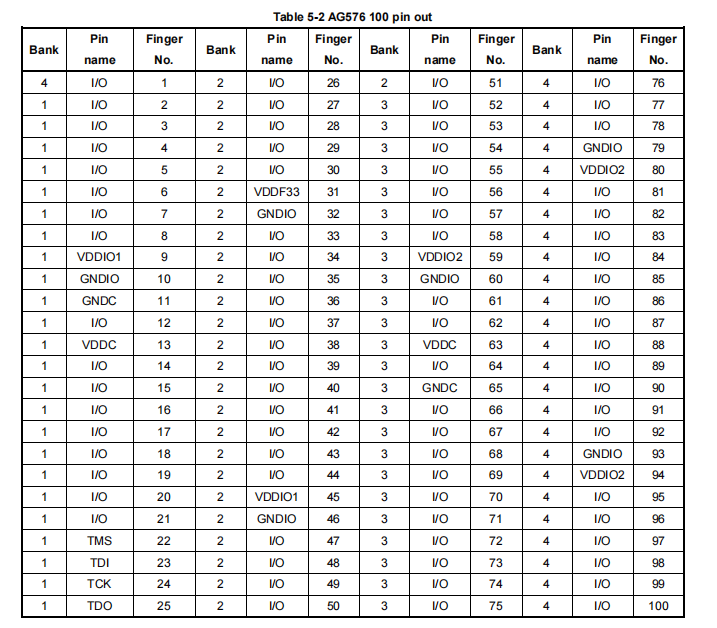

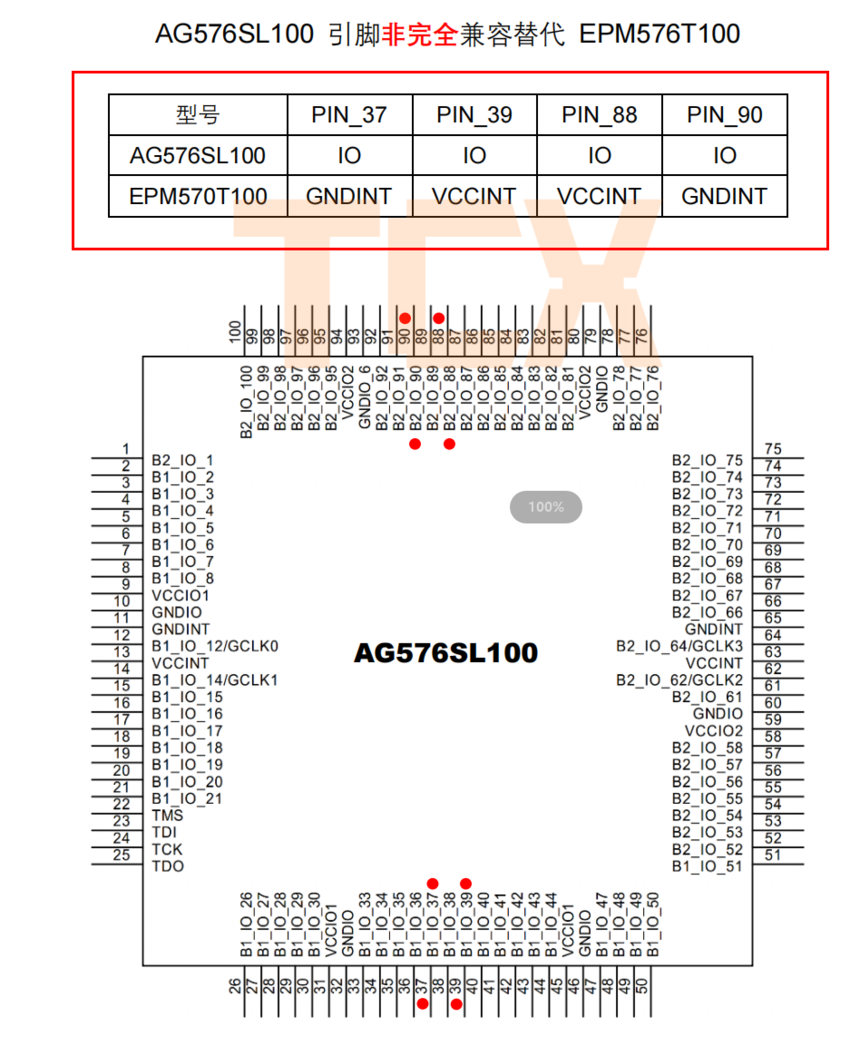

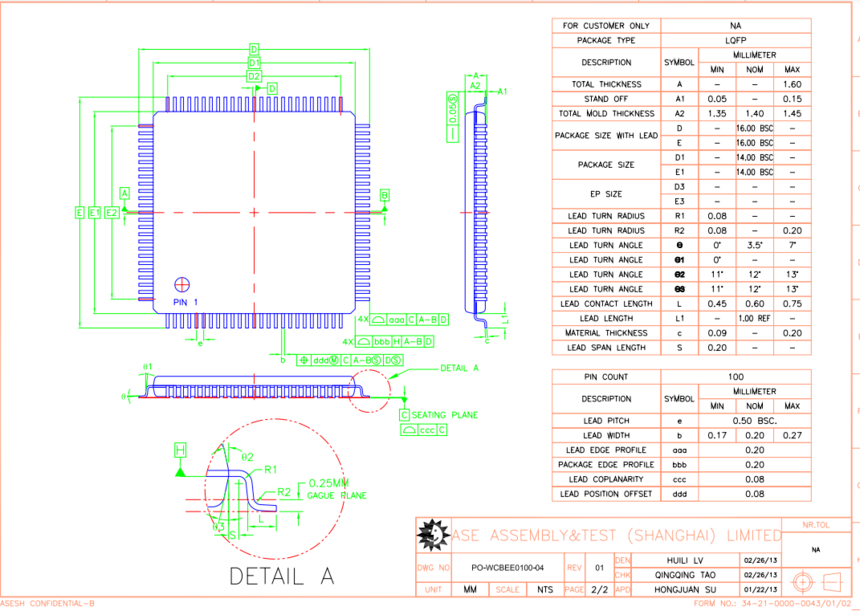

AG576 CPLDs is the low cost CPLDs. This instant-on, non-volatile CPLD family targets general-purpose and low-density logic. The logic density is 576 Logic Elements with LQFP-100 and 144 package. • Low-Cost and low-power CPLD • Instant-on, non-volatile standard compatible architecture. • Up to 4 global clock lines in the global clock network that drive throughout the entire device. • Provides programmable fast propagation delay and clock-to-output times. • Provides PLL per device, clock multiplication, and phase shifting. • UFM supports non-volatile storage up to 256 Kbits. • Supports 3.3-V, 2.5-V, 1.8-V, and 1.5-V logic level • Programmable slew rate, drive strength, bus-hold, programmable pull-up resistors, open-drain output, Schmitt triggers and programmable input delay. • Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry complaint with IEEE Std. 1149.1-1990 • ISP circuitry compliant with IEEE Std. 1532 • 3.3-V, 2.5-V, 1.8-V, 1.5-V LVCMOS and LVTTL standards • Emulated LVDS output (LVDS_E_3R) • Emulated RSDS output (RSDS_E_3R) AG576SL100C3ЪЧвЛПюГЌЕЭГЩБОЕФFPGAЃЌТпМзЪдДга576ИіКъЕЅдЊЃЌПЩвдЬцДњALTERAЕФEPM570T100CxN,EPM570T100IxNМлИёдЖЕЭгкЦфЫћЦЗХЦЭЌЕШзЪдДЕФFPGAЦїМўЁЃФПЧАдНРДдНЖрЕФЙЄвЕПЭЛЇбЁдёAG576SL100C3ЃЌЬсИпВњЦЗЕФзлКЯадМлБШ • ЕЭГЩБОЁЂЕЭЙІКФЕФCPLD • МДЪБЦєЖЏЁЂЗЧвзЪЇадFPGA МмЙЙЁЃ • ШЋОжЪБжгЭјТчжаЖрДя4ЬѕШЋОжЪБжгЯпЧ§ЖЏећИіЩшБИЁЃ • ЬсЙЉПЩБрГЬЕФДЋВЅбгГйКЭЪБжгЕНЪфГіЪБМфЁЃ • УПИіЦїМўЬсЙЉPLLЃЌЬсЙЉЪБжгБЖЦЕКЭвЦЯрЃЈAG256 УЛгаPLLЃЉЁЃ • UFM жЇГж 256 Kbits ЕФЗЧвзЪЇадДцДЂЁЃ • жЇГж 3.3-VЁЂ2.5-VЁЂ1.8-V КЭ 1.5-V ТпМЕчЦН • ПЩБрГЬбЙАкТЪЁЂЧ§ЖЏЧПЖШЁЂзмЯпБЃГжЁЂПЩБрГЬЩЯРЕчзшЁЂПЊТЉЪфГіЁЂЪЉУмЬиДЅЗЂЦїКЭПЩБрГЬЪфШыбгГйЁЃ • ФкжУJTAG КЭBSTЃЌЕчТЗЗћКЯ IEEE БъзМЁЃ 1149.1-1990 • ISP ЕчТЗЗћКЯ IEEE БъзМ. 1532 • 3.3-VЁЂ2.5-VЁЂ1.8-VЁЂ1.5-V LVCMOS КЭ LVTTL БъзМ • ЗТец LVDS ЪфГі (LVDS_E_3R) • ЗТец RSDS ЪфГі (RSDS_E_3R) • ЙЄзїНсЮТЗЖЮЇЮЊ -40 жС 100 ЁуC

上一篇AG256SL100下一篇AG576SL144 |